# HY2550 Series Datasheet

Protection IC for 3/4/5-cell Li+ Battery

## Protection IC for 3/4/5-Cell Li+ Battery

## **Table of Contents**

| 1. | GENERAL DESCRIPTION                                      | 4  |

|----|----------------------------------------------------------|----|

| 2. | FEATURES                                                 | 4  |

| 3. | APPLICATIONS                                             | 5  |

| 4. | BLOCK DIAGRAM                                            | 6  |

| 5. | PIN DEFINITION                                           | 7  |

| 6. | ELECTRICAL CHARACTERISTICS                               | 9  |

| 7. | TEST CIRCUIT                                             | 12 |

| 8  | DESCRIPTION OF OPERATION                                 | 15 |

| 9  | TIMING DIAGRAM                                           | 19 |

| 10 | EXAMPLE OF APPLICATION CIRCUIT FOR BATTERY PROTECTION IC | 22 |

| 11 | TEMPERATURE CHARACTERISTICS (TYPICAL VALUE)              | 25 |

| 12 | ORDERING INFORMATION                                     | 28 |

| 13 | PACKAGE INFORMATION                                      | 29 |

| 14 | TAPE & REEL INFORMATION                                  | 30 |

| 15 | PEVISION PECOPD                                          | 21 |

## Protection IC for 3/4/5-Cell Li+ Battery

#### Attention:

- 1 HYCON Technology Corp. reserves the right to change the content of this datasheet without further notice. For most up-to-date information, please constantly visit our website: http://www.hycontek.com.

- 2 · HYCON Technology Corp. is not responsible for problems caused by figures or application circuits narrated herein whose related industrial properties belong to third parties.

- 3 Specifications of any HYCON Technology Corp. products detailed or contained herein stipulate the performance, characteristics, and functions of the specified products in the independent state. We does not guarantee of the performance, characteristics, and functions of the specified products as placed in the customer's products or equipment. Constant and sufficient verification and evaluation is highly advised.

- 4 Please note the operating conditions of input voltage, output voltage and load current and ensure the IC internal power consumption does not exceed that of package tolerance. HYCON Technology Corp. assumes no responsibility for equipment failures that resulted from using products at values that exceed, even momentarily, rated values listed in products specifications of HYCON products specified herein.

- 5 Notwithstanding this product has built-in ESD protection circuit, please do not exert excessive static electricity to protection circuit.

- 6 Products specified or contained herein cannot be employed in applications which require extremely high levels of reliability, such as device or equipment affecting the human body, health/medical equipments, security systems, or any apparatus installed in aircrafts and other vehicles.

- 7 Despite the fact that HYCON Technology Corp. endeavors to enhance product quality as well as reliability in every possible way, failure or malfunction of semiconductor products may happen. Hence, users are strongly recommended to comply with safety design including redundancy and fire-precaution equipments to prevent any accidents and fires that may follow.

- 8 \ Use of the information described herein for other purposes and/or reproduction or copying without the permission of HYCON Technology Corp. is strictly prohibited.

#### Protection IC for 3/4/5-Cell Li+ Battery

#### 1. General Description

HY2550 Series is a protection IC for safety of 3-cell /4-cell/5-cell lithium ion and lithium polymer rechargeable batteries. The protection IC integrates accurate voltage detection and protection delay circuitry for best battery protection purpose.

#### 2. Features

The features that whole series of HY2550 comprised are as follows:

(1) High-accuracy voltage detection for each cell:

Overcharge detection voltage n (n = 1 to 5)

Overcharge release voltage n (n = 1 to 5)

Overdischarge detection voltage n (n = 1 to 5)

Overdischarge release voltage n (n = 1 to 5)

Overdischarge release voltage n (n = 1 to 5)

Overdischarge release voltage n (n = 1 to 5)

Overdischarge release voltage n (n = 1 to 5)

Overdischarge release voltage n (n = 1 to 5)

Overdischarge release voltage n (n = 1 to 5)

Overdischarge release voltage n (n = 1 to 5)

(2) Charge overcurrent protection:

Charge overcurrent detection voltage -0.05V to -0.35V

Accuracy: ±25mV

(3) Three-level discharge overcurrent protection:

Overcurrent detection voltage 1 0.05V to 0.35V Accuracy: ±25mV

Overcurrent detection voltage 2 0.10V to 0.50V (50mV step) Accuracy: ±50mV

Overcurrent detection voltage 3 VC1 – 0.1V to VC1-1.2V (50mV step) Accuracy: ±100mV

#### (4) Delay time:

Delay times are set by external capacitors respectively at CCT pin and CDT pin for overcharge detection, /charge overcurrent detection and overdischarge detection/discharge overcurrent detection voltage 1. Delay times are set internally for discharge overcurrent detection voltage 2 (1ms) and discharge overcurrent detection 3 (300µs).

#### (5) Cell number selection:

SEL pin is used to select either 3 battery cells in use or 4 battery cells in use. SEL5 pin is used to select 5 battery cells in use when SEL pin is also set to "1"

(6) Charge/discharge operation can be controlled via the CTL pin.

(7) 0V Battery Charge inhibition.

(8) High voltage withstand range: Absolute maximum rated level: 28V

(9) Wide operating voltage range: Maximum operation voltage level: 26V

(10) Wide operating temperature range:  $-40^{\circ}$ C to  $+85^{\circ}$ C

(11) Low current consumption

## Protection IC for 3/4/5-Cell Li+ Battery

• Operation mode  $12\mu A \text{ typ.}, 30\mu A \text{ max.} (V_{Cn} = 3.5V)$

Power-down mode 1.2 $\mu$ A typ., 2.0 $\mu$ A max. ( $V_{Cn} = 2.0V$ )

(12) Small package: 16-pin TSSOP

(13) Halogen free green product

Note: \*1. Overcharge hysteresis voltage can be selected from 0 to 0.4V in 25mV steps.

(Overcharge hysteresis voltage = Overcharge detection voltage - Overcharge release voltage)

\*2. Overdischarge hysteresis voltage can be selected from 0 to 0.7V in 50mV steps.

(Overdischarge hysteresis voltage = Overdischarge release voltage - Overdischarge detection voltage)

#### 3. Applications

• 3-cell / 4-cell/ 5-cell lithium ion rechargeable battery pack

• 3-cell / 4-cell/ 5-cell lithium polymer rechargeable battery pack

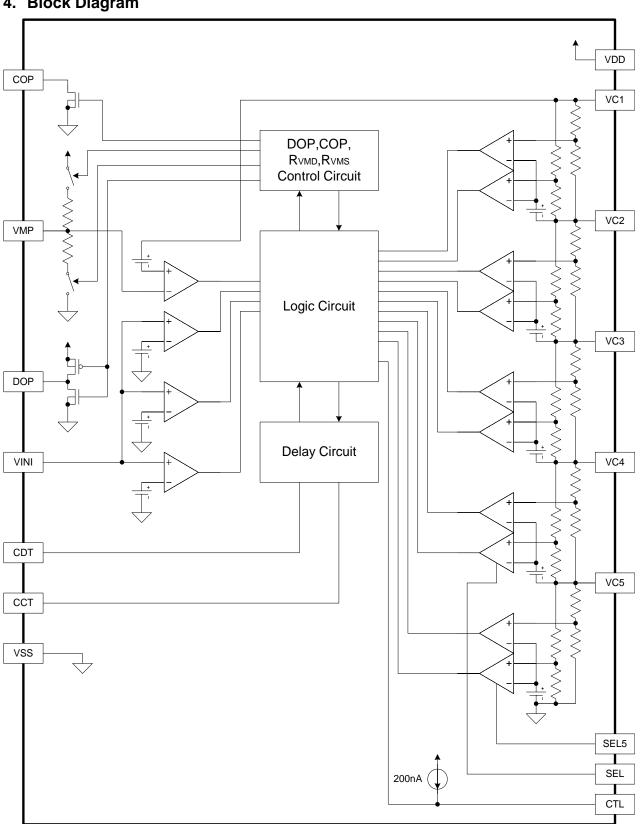

## 4. Block Diagram

## Protection IC for 3/4/5-Cell Li+ Battery

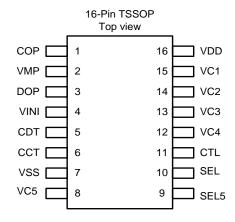

#### 5. Pin Definition

5.1 TSSOP-16 Diagram

#### 5.2 Pinout I/O Description

| Pin | Symbol | Description                                                                                                                   |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------|

| 1   | COP    | FET gate connection pin for charge control (Nch open drain output)                                                            |

| 2   | VMP    | Pin for voltage detection between VC1 and VMP (Pin for discharge overcurrent detection 3)                                     |

| 3   | DOP    | FET gate connection pin for discharge control FET (CMOS output)                                                               |

| 4   | VINI   | Pin for voltage detection between VSS and VINI (Pin for discharge overcurrent detection 1,2 and charge overcurrent detection) |

| 5   | CDT    | Capacitor connection pin for overdischarge delay and discharge overcurrent detection 1 delay.                                 |

| 6   | CCT    | Capacitor connection pin for overcharge delay and charge overcurrent detection delay.                                         |

| 7   | VSS    | Input pin for negative power supply, Connection pin for battery 5's negative voltage                                          |

| 8   | VC5    | Connection pin for battery 4's negative voltage, Connection pin for battery 5's positive voltage                              |

| 9   | SEL5   | Pin for selecting 5-series VSS level: 3-series and 4-series cell, VDD level: 5-series cell                                    |

| 10  | SEL    | Pin for switching 3-series or 4-series cell VSS level: 3-series cell, VDD level: 4-series cell and 5-series cell              |

| 11  | CTL    | Control of charge FET and discharge FET                                                                                       |

| 12  | VC4    | Connection pin for battery 3's negative voltage, Connection pin for battery 4's positive voltage                              |

| 13  | VC3    | Connection pin for battery 2's negative voltage, Connection pin for battery 3's positive voltage                              |

| 14  | VC2    | Connection pin for battery 1's negative voltage, Connection pin for battery 2's positive voltage                              |

| 15  | VC1    | Connection pin for battery 1's positive voltage                                                                               |

| 16  | VDD    | Input pin for positive power supply, Connection pin for battery 1's positive voltage                                          |

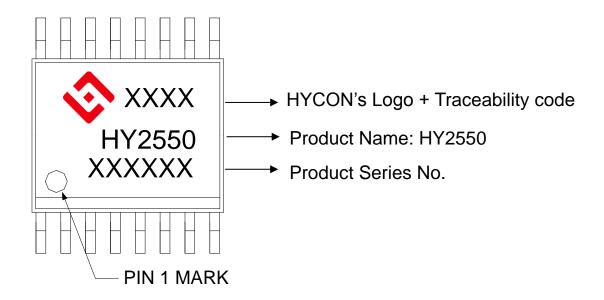

#### 5.3 Package marking information

## Protection IC for 3/4/5-Cell Li+ Battery

#### 6. Electrical Characteristics

6.1 Absolute Maximum Rating

(VSS = 0V, Ta=25  $^{\circ}$ C unless indicated otherwise)

| ltem                              | Symbol          | Specification      | Unit                 |

|-----------------------------------|-----------------|--------------------|----------------------|

| Input voltage between VDD and VSS | V <sub>DS</sub> | VSS-0.3 to VSS+28  | V                    |

| VC1 pin input voltage             | VC1             | VC2-0.3 to VC2+5.5 | V                    |

| VC2 pin input voltage             | VC2             | VC3-0.3 to VC3+5.5 | V                    |

| VC3 pin input voltage             | VC3             | VC4-0.3 to VC4+5.5 | V                    |

| VC4 pin input voltage             | VC4             | VC5-0.3 to VC5+5.5 | V                    |

| VC5 pin input voltage             | VC5             | VSS-0.3 to VSS+5.5 | V                    |

| VINI pin input voltage            | VINI            | VSS-0.3 to VSS+5.5 | V                    |

| CTL pin input voltage             | CTL             | VSS-0.3 to VDD+0.3 | V                    |

| SEL pin input voltage             | SEL             | VSS-0.3 to VDD+0.3 | V                    |

| SEL5 pin input voltage            | SEL5            | VSS-0.3 to VDD+0.3 | V                    |

| VMP Input pin voltage             | VMP             | VSS-0.3 to VSS+28  | V                    |

| COP pin output voltage            | COP             | VSS-0.3 to VSS+28  | V                    |

| DOP pin output voltage            | DOP             | VSS-0.3 to VDD+0.3 | V                    |

| Operating Temperature Range       | TOP             | -40 to +85         | $^{\circ}\mathbb{C}$ |

| Storage Temperature Range         | TST             | -40 to +125        | $^{\circ}\mathbb{C}$ |

| Tolerant Power Consumption        | PD              | 400                | mW                   |

#### 6.2 Electrical Parameters

(VSS = 0V, Ta=25  $^{\circ}$ C unless indicated otherwise)

| Item Symbol                                              |                   | Condition                                             | Min.                      | Тур.              | Max.                      | Unit      |

|----------------------------------------------------------|-------------------|-------------------------------------------------------|---------------------------|-------------------|---------------------------|-----------|

| <b>Detection Voltage</b>                                 |                   |                                                       |                           |                   |                           |           |

| Overcharge<br>detection voltage n<br>(n = 1 to 5)        | Vcun              | V <sub>CU</sub> n = 3.9V ~ 4.6V<br>adjustable         | V <sub>CUn</sub> - 0.025  | Vcun              | V <sub>C</sub> un + 0.025 | V         |

| Overcharge release voltage n (n = 1 to 5)                | V <sub>CRn</sub>  | VCRn = 3.8V ~ 4.6V adjustable                         | V <sub>CRn</sub> – 0.050  | $V_{CRn}$         | V <sub>CRn</sub> + 0.050  | V         |

| Overdischarge<br>detection voltage n<br>(n = 1 to 5)     | $V_{DLn}$         | V <sub>DL</sub> n = 2.0V ~ 3.0V adjustable            | V <sub>DLn</sub> – 0.080  | $V_{DLn}$         | V <sub>DL</sub> n + 0.080 | V         |

| Overdischarge release voltage n (n = 1 to 5)             | $V_{DRn}$         | V <sub>DR</sub> n = 2.0V ~ 3.4V adjustable            | V <sub>DRn</sub> – 0.100  | $V_{DRn}$         | V <sub>DRn</sub> + 0.100  | ٧         |

| Overcurrent detection voltage 1                          | V <sub>IOV1</sub> | V <sub>IOV1</sub> = 0.05V ~ 0.35V adjustable          | V <sub>IOV1</sub> – 0.025 | V <sub>IOV1</sub> | V <sub>IOV1</sub> + 0.025 | V         |

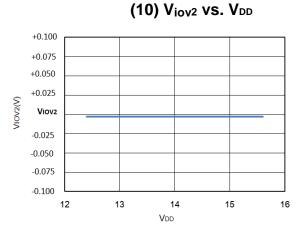

| Overcurrent detection voltage 2                          | V <sub>IOV2</sub> | $V_{IOV2} = 0.1V \sim 0.5V$ adjustable                | V <sub>IOV2</sub> – 0.05  | V <sub>IOV2</sub> | V <sub>IOV2</sub> + 0.05  | V         |

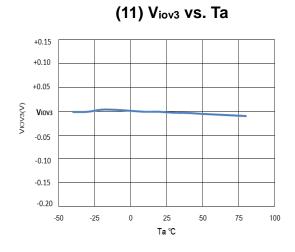

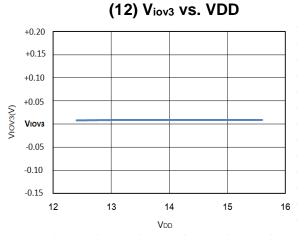

| Overcurrent detection voltage 3                          | V <sub>IOV3</sub> | V <sub>IOV3</sub> = VC1-0.1V ~<br>VC1-1.2V adjustable | VC1-1.5                   | VC1-1.2           | VC1-0.9                   | V         |

| Charge overcurrent detection voltage                     | V <sub>CIP</sub>  | $V_{CIP}$ = -0.05V ~ -0.35V adjustable                | V <sub>CIP</sub> – 0.025  | Vcip              | V <sub>CIP</sub> + 0.025  | V         |

| Temperature coefficient for overcharge detection voltage | TC <sub>OE1</sub> | Ta = 0°C ~ 50°C *1                                    | -1                        | 0                 | 1                         | mV/<br>°C |

| Temperature coefficient for                              | T <sub>COE2</sub> | Ta = 0°C ~ 50°C *1                                    | -0.5                      | 0                 | 0.5                       | mV/<br>℃  |

## Protection IC for 3/4/5-Cell Li+ Battery

| Item                     | Symbol            | Condition              | Min. | Тур. | Max. | Unit  |

|--------------------------|-------------------|------------------------|------|------|------|-------|

| overcurrent              |                   |                        |      |      |      |       |

| detection voltage 1      |                   |                        |      |      |      |       |

| Delay Time               |                   |                        |      |      |      |       |

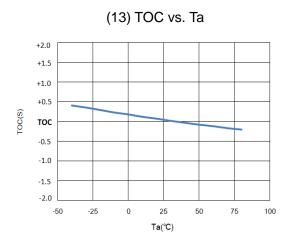

| Overcharge               | Toc               | CCT pin                | 0.5  | 1    | 1.5  |       |

| detection delay time     | TOC               | capacitance=0.1µF      | 0.5  | · ·  | 1.5  | S     |

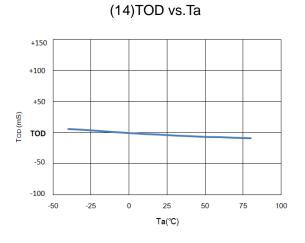

| Overdischarge            | T <sub>OD</sub>   | CDT pin                | 50   | 100  | 150  | ms    |

| detection delay time     | 100               | capacitance=0.1µF      |      | 100  | 150  | 1113  |

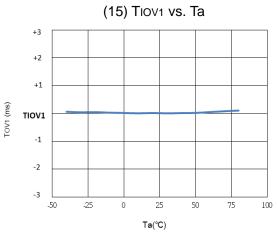

| Overcurrent              |                   | CDT pin                |      |      |      |       |

| detection delay time     | T <sub>IOV1</sub> | capacitance=0.1µF      | 5    | 10   | 15   | ms    |

| 1                        |                   | т.,                    |      |      |      |       |

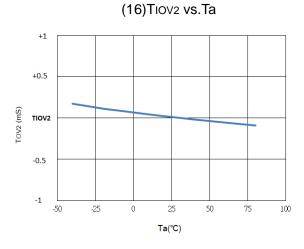

| Overcurrent              | _                 |                        | 0.4  | _    | 4.0  |       |

| detection delay time     | T <sub>IOV2</sub> |                        | 0.4  | 1    | 1.6  | ms    |

| 2<br>Overcurrent         |                   |                        |      |      |      | +     |

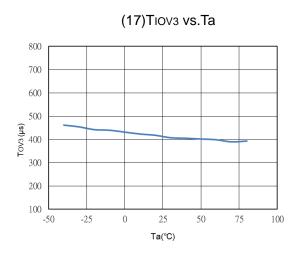

| detection delay time     | T <sub>IOV3</sub> | FET gate capacitance = | 100  | 300  | 600  | 116   |

| 3                        | 11003             | 2000pF.                | 100  | 300  | 000  | μs    |

| Charge overcurrent       |                   | CCT pin                |      |      |      |       |

| detection delay time     | T <sub>CIP</sub>  | capacitance=0.1µF      | 5    | 10   | 15   | ms    |

| 0V Battery Charge F      | unction           | '                      |      | •    |      |       |

| 0 V battery charge       |                   | 0.7/1 # 1 1            |      |      |      |       |

| starting charger         | V <sub>0CHA</sub> | 0 V battery charging   | 3.0  |      |      | V     |

| voltage                  |                   | available              |      |      |      |       |

| Internal Resistance      |                   |                        |      |      |      |       |

| Resistance between       | R <sub>VMD</sub>  |                        | 0.5  | 1    | 1.5  | ΜΩ    |

| VMP and VDD              | IXVMD             |                        | 0.5  | '    | 1.5  | 10122 |

| Resistance between       | R <sub>VMS</sub>  |                        | 0.45 | 0.9  | 1.8  | МΩ    |

| VMP and VSS              | T V IVIS          |                        | 0.10 | 0.0  | 1.0  | 17132 |

| Input Voltage            | T                 | T T                    |      | ī    | I    |       |

| Operating voltage        |                   |                        | _    |      |      | l     |

| between VDD and          | VDSOP             |                        | 3    | -    | 26   | V     |

| VSS                      |                   |                        |      |      |      | 1     |

| CTL input voltage<br>"H" | V <sub>CTLH</sub> |                        | 4.0  | -    | -    | V     |

| CTL input voltage        |                   |                        |      |      |      | _     |

| "L"                      | $V_{CTLL}$        |                        | -    | -    | 2.0  | V     |

| SEL input voltage        |                   |                        |      |      |      | 1     |

| "H"                      | Vselh             |                        | 4.0  | -    | -    | V     |

| SEL input voltage        |                   |                        |      |      |      |       |

| "L"                      | V <sub>SELL</sub> |                        | -    | -    | 2.0  | V     |

| Input Current            |                   |                        |      | -    | -    | •     |

| Current                  |                   |                        |      |      |      |       |

| consumption during       | I <sub>OPE</sub>  | V1=V2=V3=V4=V5=3.5V    |      | 12   | 30   | μΑ    |

| operation                |                   |                        |      |      |      |       |

| Current                  |                   |                        |      |      |      |       |

| consumption during       | ,                 |                        |      | 1.2  | 2.0  | μΑ    |

| power-down               |                   |                        |      |      |      |       |

| VC1 pin current          | Ivc <sub>1</sub>  | V1=V2=V3=V4=V5=3.5V    |      | 3.6  | 6.0  | μA    |

| VC2 pin current          | I <sub>VC2</sub>  | V1=V2=V3=V4=V5=3.5V    | -0.3 | 0    | 0.3  | μA    |

| VC3 pin current          | I <sub>VC3</sub>  | V1=V2=V3=V4=V5=3.5V    | -0.3 | 0    | 0.3  | μΑ    |

## Protection IC for 3/4/5-Cell Li+ Battery

| Item                                      | Symbol            | Condition                        | Min. | Тур. | Max. | Unit |

|-------------------------------------------|-------------------|----------------------------------|------|------|------|------|

| VC4 pin current                           | I <sub>VC4</sub>  | V1=V2=V3=V4=V5=3.5V              | -0.3 | 0    | 0.3  | μΑ   |

| CTL pin current "H"                       | Істьн             | V1=V2=V3=V4=V5=3.5V,<br>CTL=VDD  |      |      | 0.1  | μΑ   |

| CTL pin current "L"                       | ICTLL             | V1=V2=V3=V4=V5=3.5V,<br>CTL=VSS  | -0.4 | -0.2 |      | μΑ   |

| SEL pin current "H"                       | I <sub>SELH</sub> | V1=V2=V3=V4=V5=3.5V,<br>SEL=VDD  |      |      | 0.1  | μΑ   |

| SEL pin current "L" ISELL                 |                   | V1=V2=V3=V4=V5=3.5V,<br>SEL=VSS  | -0.1 |      |      | μΑ   |

| SEL5 pin current "H" ISEL5H               |                   | V1=V2=V3=V4=V5=3.5V,<br>SEL5=VDD |      |      | 0.1  | μΑ   |

| SEL5 pin current "L" ISEL5L               |                   | V1=V2=V3=V4=V5=3.5V,<br>SEL5=VSS | -0.1 |      |      | μA   |

| Output Current                            |                   |                                  |      |      |      |      |

| COP pin leakage current                   | Ісон              | V <sub>COP</sub> =26V            |      |      | 0.1  | μΑ   |

| COP pin sink current                      | Icol              | V <sub>COP</sub> =VSS+0.5V       | 5    |      |      | μΑ   |

| DOP pin source current IDOH VDOP=VDD-0.5V |                   | V <sub>DOP</sub> =VDD-0.5V       | 5    |      |      | μA   |

| DOP pin sink current                      | I <sub>DOL</sub>  | V <sub>DOP</sub> =VSS+0.5V       | 5    |      |      | μΑ   |

## **Description:**

<sup>\*1.</sup> The parameters within this temperature range are design guarantee values instead of screened values from high, low temperature measurement.

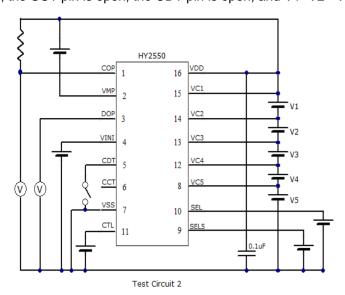

#### 7. Test Circuit

- 7.1 The current at the VSS pin when V1= V2= V3= V4= V5=3.5 V and VVMP= VDD is the a current consumption during operation (IOPE)

- 7.2 The current at the VSS pin when V1 = V2 = V3 = V4 = V5 = 2.0 V, and VVMP = VSS is the current consumption during power-down (IPDN)  $^{\circ}$

Test Circuit 1

7.3 Overcharge Detection Voltage (VCUn) ` Overcharge Release Voltage (VCRn) ` Overdischarge Detection Voltage (VDLn) ` Overdischarge Release Voltage(VDRn) ` Overcurrent Detection Voltage 1 (VIOV1) ` Overcurrent Detection Voltage2(VIOV2) ` Overcurrent Detection Voltage3(VIOV3) ` CTL Input Voltage "H", CTL Input Voltage "L", SEL Input Voltage "H", SEL Input Voltage "L" (Test Circuit 2).

Confirm that the COP pin and DOP pin are low(VDD x0.1 V or lower) when VVMP= VSEL=VDD, VINI=VCTL=VSS, the CCT pin is open, the CDT pin is open, and V1=V2=V3=V4=V5=3.5 V.

7.3.1 Overcharge Detection Voltage (VCUn) · Overcharge Release Voltage (VCRn)

The overcharge detection voltage (VCUn) is the voltage of V1 when the voltage of the COP

### Protection IC for 3/4/5-Cell Li+ Battery

pin is "H" (VDD x 0.9 V or more) after the V1 voltage has been gradually increased starting at the initial status. The overcharge release voltage (VCRn) is the voltage of V1 when the voltage at the COP pin is "L" after the V1 voltage has been gradually decreased.

#### 7.3.2 Overdischarge Detection Voltage (VDLn), Overdischarge Release Voltage (VDRn)

The overdischarge detection voltage (VDLn) is the voltage of V1 when the voltage of the DOP pin is after the V1 voltage has been gradually decreased starting at the initial status. The overdischarge  $\circ$  release voltage (VDR1) is the voltage of V1 when the voltage at the DOP pin is "L" after the V1 voltage has been gradually increased  $\circ$  When the voltage of Vn (n=2 to 5) is changed, the overcharge detection voltage (VCUn), overcharge release voltage (VCRn), overdischarge detection voltage (VDLn), and

overdischarge release voltage (VDRn) can be determined in the same way as when n =1.

#### 7.3.3 Overcurrent Detection Voltage 1 (Viova)

Overcurrent detection voltage 1 (V<sub>IOV1</sub>) is the voltage of the VINI pin when the voltage of the DOP pin1 (V<sub>IOV1</sub>) is "H" after the VINI pin voltage has been gradually increased starting at the initial status.

#### 7.3.4 Overcurrent Detection Voltage2 (Viov2)

Overcurrent detection voltage 2 ( $V_{IOV2}$ ) is the voltage of the VINI pin when the voltage of the DOP pin is "H" after the voltage of the CDT pin was set to  $V_{SS}$  following the initial status and the voltage of the VINI pin has been gradually decreased.

#### 7.3.5 Overcurrent Detection Voltage3 (Viov3)

Overcurrent detection voltage 3 (VIOV3) is the voltage difference between VVC1 and VVMP (VVC1 -VVMP) when the voltage of the DOP pin is "H" after the VMP voltage has been gradually decreased starting at the initial status.

#### 7.3.6 Overcharge Current Detection Voltage (VCIP)

Overcharge current detection voltage 1 (VCIP) is the voltage of the VINI pin when the voltage of the COP pin1 (VCIP) is "H" after the VINI pin voltage has been gradually increased starting at the initial status.

#### 7.4 CTL Input Voltage "H" (VCTLH) . CTL Input Voltage "L" (VCTLL)

The CTL input voltage "H" (VCTLH) is the voltage of CTL when the voltages at the COP and DOP pins are "H" after the CTL voltage has been gradually increased starting at the initial status. The CTL input voltage "L" (VCTL) is the voltage of CTL when the voltages at the COP and DOP pins are "L" after the CTL voltage has been gradually decreased.

#### 7.5 SEL Input Voltage "H" (VSELH) · SEL Input Voltage "L" (VSELL)

Apply 0 V to V4 in the initial status and confirm that the DOP pin is "H". The SEL input voltage "L"(VSELL) is the voltage of the SEL pin when the voltage at the DOP pin is "L" after the SEL voltage has been gradually decreased. The SEL input voltage "H" (VSELH) is the voltage of the SEL pin when the voltage of the DOP pin is "H" after the SEL voltage has been gradually increased.

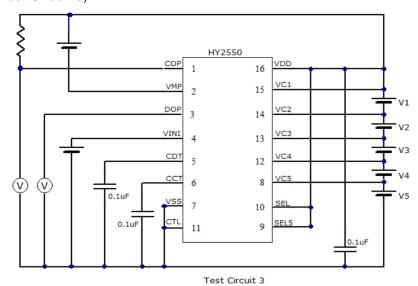

## 7.6 Overcharge Detection Delay Time, Overcurrent Detection Delay Time 1, Overcurrent Detection Delay Time 2, Overcurrent Detection Delay Time 3 (Test Circuit 3)

Confirm that the COP pin and DOP pin are "L" when VVMP =VDD, VINI =VSS, and V1=V2=V3 =V4= V5=3.5 V (this status is referred to as the initial status.

#### 7.6.1 Overcharge Detection Delay Time (toc)

The overcharge detection delay time (tOC) is the time it takes for the voltage of the COP pin to change from "L" to "H" after the voltage of V1 is instantaneously changed to 4.5 V from the initial status.

#### 7.6.2 Overdischarge Detection Delay Time (top)

The overdischarge detection delay time (tOD) is the time it takes for the voltage of the DOP pin to change from "L" to "H" after the voltage of V1 is instantaneously changed to 1.5 V from the initial status.

#### 7.6.3 Overcurrent Detection Delay Time1 (tiov1)

Overcurrent detection delay time 1 (tIOV1) is the time it takes for the voltage of the DOP pin to change from "L" to "H" after the voltage of the VINI pin is instantaneously changed to 0.4 V from the initial status.

#### Protection IC for 3/4/5-Cell Li+ Battery

#### 7.6.4 Overcurrent Detection Delay Time 2 (tiov2)

Overcurrent detection delay time 2 (t<sub>IOV2</sub>) is the time it takes for the voltage of the DOP pin to change from "L" to "H" after the voltage of the VINI pin is instantaneously changed to VIOV2 max. +0.2 V from the initial status.

#### 7.6.5 Overcurrent Detection Delay Time 3 (tiov3)

Overcurrent detection delay time 3 (t<sub>IOV3</sub>) is the time it takes for the voltage of the DOP pin to change from "L" to "H" after the voltage of the VMP pin is instantaneously changed to VIOV3 min. -0.2 V from the initial status.

#### 8. Description of Operation

#### 8.1 Normal Status

When the voltage of each of the batteries is in the range from  $V_{DLn}$  to  $V_{CUn}$  and the discharge current is lower than the specified value (the VINI pin voltage is higher than  $V_{CIP}$ , the VINI pin voltage is lower than  $V_{IOV1}$  and  $V_{IOV2}$ , and the VMP pin voltage is higher than  $V_{IOV3}$ ), the charging and discharging FETs are turned on.

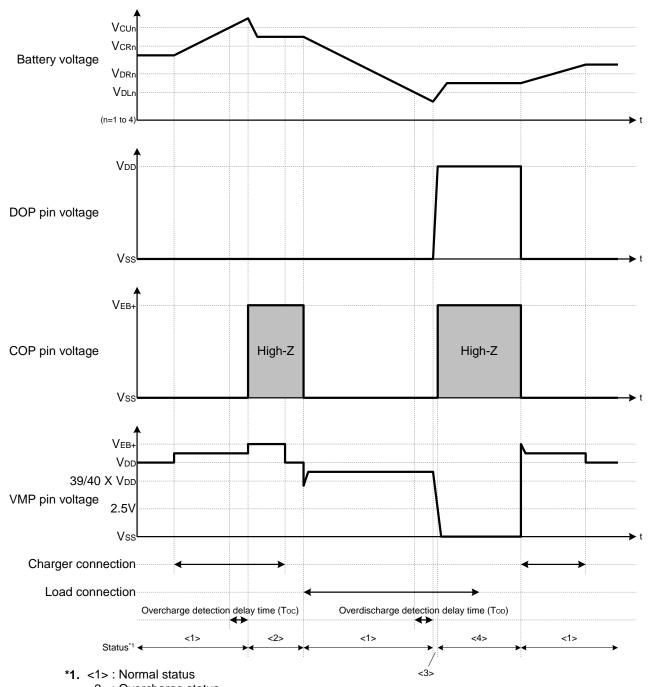

#### 8.2 Overcharge Status

When the voltage of one of the batteries becomes higher than V<sub>CUn</sub> and the state continues for T<sub>OC</sub> or longer, the COP pin becomes high impedance. The COP pin is pulled up to the EB+ pin voltage by an external resistor, and the charging FET is turned off to stop charging. This is called the overcharge status. The overcharge status is released when one of the following two conditions holds.

- (1) The voltage of each of the batteries becomes  $V_{\text{CRn}}$  or lower.

- (2) The voltage of each of the batteries is  $V_{CUn}$  or lower, and the VMP pin voltage is 39 / 40 x VDD or lower (a load is connected and discharging is started via the body diode of the charging FET).

#### 8.3 Overdischarge Status

When the voltage of one of the batteries becomes lower than  $V_{DLn}$  and the state continues for  $T_{OD}$  or longer, the DOP pin voltage becomes VDD level, and the discharging FET is turned off to stop discharging. This is called the overdischarge status.

#### 8.4 Power-down Function

When the overdischarge status is reached, the VMP pin is pulled down to the VSS level by the internal R<sub>VMS</sub> resistor of the IC. When the VMP pin voltage is 2.5V or lower, the power-down function starts to operate and almost every circuit in the HY2550 Series stops working. The conditions of each output pin are as follows.

(1) COP pin : High-Z(2) DOP pin : VDD

## HY2550 Series Protection IC for 3/4/5-Cell Li+ Battery

The power-down function is released when the following condition holds.

(1) The VMP pin voltage is 2.5V or higher.

The overdischarge status is released when the following two conditions hold.

- (1) In case the VMP pin voltage is 2.5V or higher and the VMP pin voltage is lower than VDD, the overdischarge status is released when the voltage of each of the batteries is V<sub>DRn</sub> or higher.

- (2) In case a charger is connected, the overdischarge hysteresis is released. And the overdischarge status is released when the voltage of each of the batteries is V<sub>DLn</sub> or higher.

## Protection IC for 3/4/5-Cell Li+ Battery

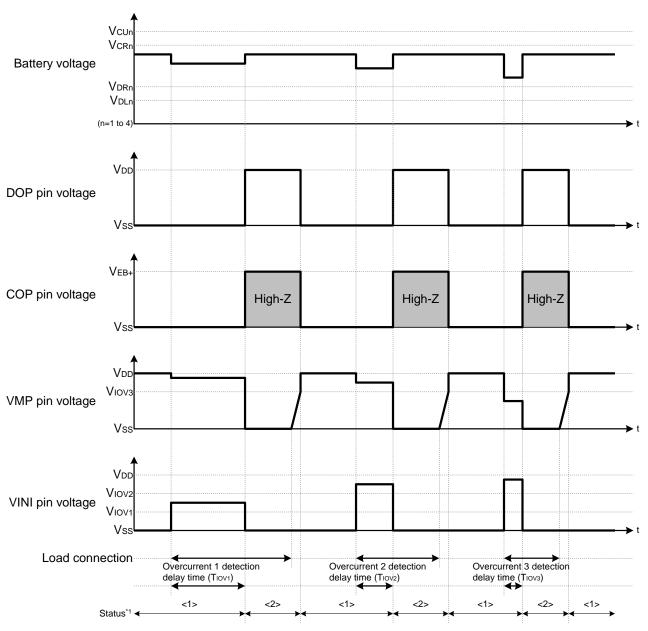

#### 8.5 Discharge Overcurrent Status

The HY2550 Series has three overcurrent detection levels (VIOV1, VIOV2, and VIOV3) and three overcurrent detection delay times (T<sub>IOV1</sub>, T<sub>IOV2</sub>, and T<sub>IOV3</sub>) corresponding to each overcurrent detection level. When the discharging current becomes higher than the specified value (the voltage between VINI and VSS is greater than V<sub>IOV1</sub>) and the state continues for T<sub>IOV1</sub> or longer, the HY2550 Series enters the overcurrent status, in which the DOP pin voltage becomes VDD level to turn off the discharging FET to stop discharging, the COP pin becomes high impedance and is pulled up to the EB+ pin voltage to turn off the charging FET to stop charging, and the VMP pin is pulled up to the VDD voltage by the internal resistor (R<sub>VMD</sub>). Operation of overcurrent detection level 2 (V<sub>IOV2</sub>) and overcurrent detection delay time 2  $(T_{IOV2})$  is the same as for  $V_{IOV1}$  and  $T_{IOV1}$ .

In the overcurrent status, the VMP pin is pulled up to the VDD level by the internal resistor in the IC (R<sub>VMD</sub> resistor). The overcurrent status is released when the following condition holds.

(1) The VMP pin voltage is  $V_{IOV3}$  or higher because a charger is connected or the load (300 K $\Omega$ or more) is released.

#### 8.6 Charge Overcurrent Status

The HY2550 Series has charge overcurrent detection levels (VCIP) and charge overcurrent detection delay times (TCIP). When the charging current becomes higher than the specified value (the voltage between VINI and VSS is lower than V<sub>CIP</sub>) and the state continues for T<sub>CIP</sub> or longer, the HY2550 Series enters the charge overcurrent status, the COP pin becomes high impedance. The COP pin is pulled up to the EB+ pin voltage by an external resistor, and the charging FET is turned off to stop charging.

The charge overcurrent status is released when the following condition holds.

(1) The VMP pin voltage is 39 / 40 x VDD or lower (disconnected the charger and a load is connected, discharging is started via the body diode of the charging FET).

#### 8.7 0V Battery Charge Function

Regarding the charging of a self-discharged battery (0 V battery), the HY2550 Series has two functions from which one should be selected.

- (1) 0 V battery charging is allowed (0 V battery charging is available.) When the charger voltage is higher than V<sub>OCHA</sub>, the 0 V battery can be charged.

- (2) 0 V battery charging is prohibited (0 V battery charging is unavailable.) When the battery voltage is Voinh or lower, the 0 V battery cannot be charged.

Caution: When the VDD pin voltage is lower than the minimum value of V<sub>DSOP</sub>, the operation of the HY2550 Series is not guaranteed.

#### 8.8 Delay Time Setting

The overcharge detection delay time (T<sub>OC</sub>) and charge overcurrent delay time (T<sub>CIP</sub>) are determined by

## Protection IC for 3/4/5-Cell Li+ Battery

the external capacitor connected to the CCT pin. The overdischarge detection delay time (Tod) and overcurrent detection delay time 1 (T<sub>IOV1</sub>) are determined by the external capacitor connected to the CDT pin. Overcurrent detection delay times 2 and 3 (T<sub>IOV2</sub>, T<sub>IOV3</sub>) are fixed internally.

|                 | min.   | typ.  | max.                          |

|-----------------|--------|-------|-------------------------------|

| $T_{OC}[s]=$    | (5.00, | 10.0, | 15.0) x C <sub>CCT</sub> [μF] |

| $T_{OD}[s]=$    | (0.50, | 1.00, | 1.50) x C <sub>CDT</sub> [μF] |

| $T_{IOV1}$ [s]= | (0.05, | 0.10, | 0.15) x $C_{CDT}$ [ $\mu F$ ] |

| $T_{CIP}[s]=$   | (0.05, | 0.10, | 0.15) x C <sub>CCT</sub> [μF] |

#### 8.9 CTL Pin

The HY2550 Series has control pins. The CTL pin is used to control the COP and DOP pin output voltages. CTL pin takes precedence over the battery protection circuit.

**Conditions Set by CTL Pin**

| CTL Pin | COP Pin          | DOP Pin          |

|---------|------------------|------------------|

| High    | High-Z           | VDD              |

| Open    | High-Z           | VDD              |

| Low     | Normal status *1 | Normal status *1 |

<sup>\*1.</sup> The status is controlled by the voltage detector.

Caution: Please note unexpected behavior might occur when electrical potential difference between the CTL pin ('L' level) and VSS is generated through the external filter (Rvss and C<sub>VSS</sub>) as a result of input voltage fluctuations.

#### 8.10 SEL&SEL5 Pin

The HY2550 Series has two SELECT pins. The SEL pin is used to switch between 3-cell and 4-cell protection and the SEL5 pin is used to select 5-cell protection. When the SEL pin and SEL5 pin are low, overdischarge detection of the V4 cell is prohibited and an overdischarge is not detected even if the V4 cell is shorted, therefore, the V4 cell can be used for 3-cell protection. The SEL pin and SEL5 pin take precedence over the battery protection circuit. Use the SEL pin & SEL5 pin at high or low.

Conditions Set by SEL Pin &SEL5 pin

| SEL Pin | SEL5 Pin | Condition         |

|---------|----------|-------------------|

| High    | High     | 5-cell protection |

| High    | Low      | 4-cell protection |

| Low     | Low      | 3-cell protection |

| Open    | Open     | Undefined         |

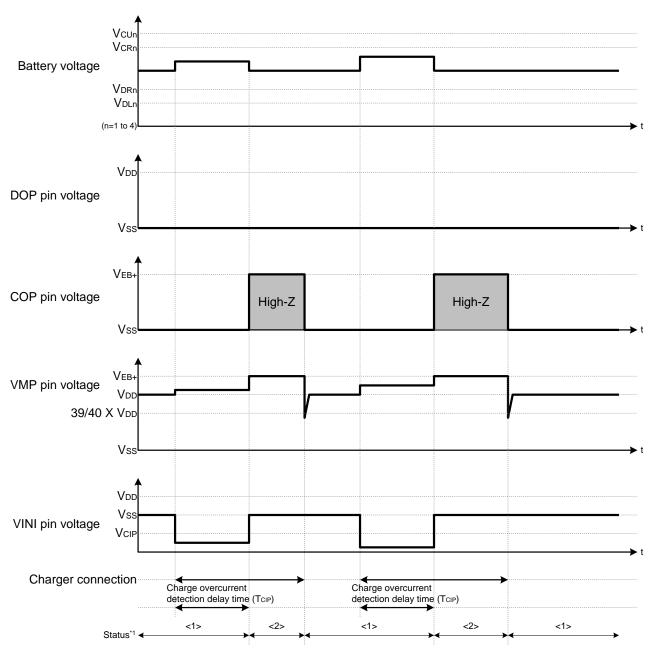

## 9. Timing Diagram

## (1) Overcharge Detection and Overdischarge Detection

<2> : Overcharge status

<3>: Overdischarge status

<4> : Power-down status

## HYCON TECHNOLOGY

#### (2) Discharge Overcurrent Detection

\*1. <1>: Normal status

<2> : Discharge overcurrent status

#### (3) Charge Overcurrent Detection

\*1. <1>: Normal status

<2> : Charge overcurrent status

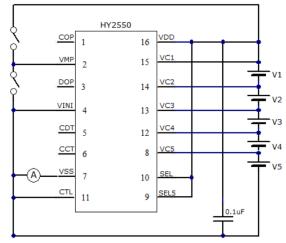

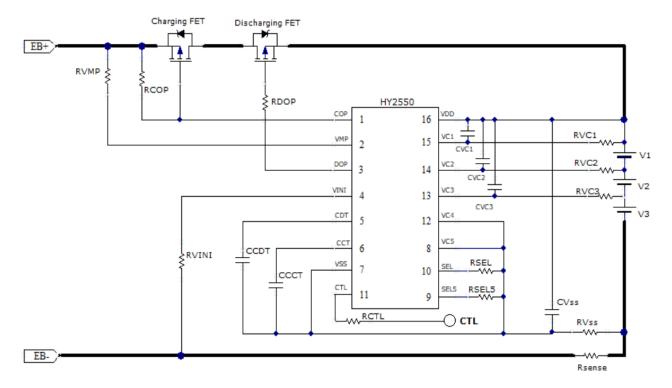

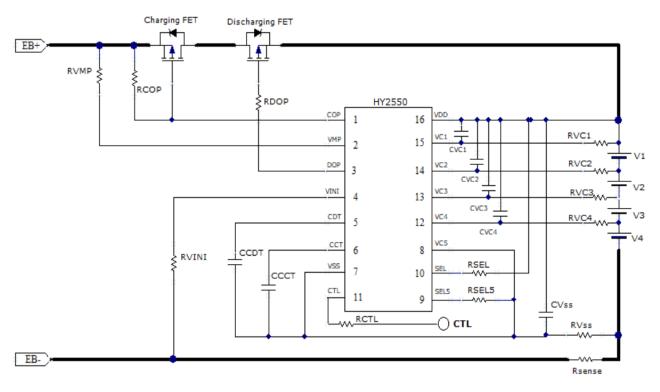

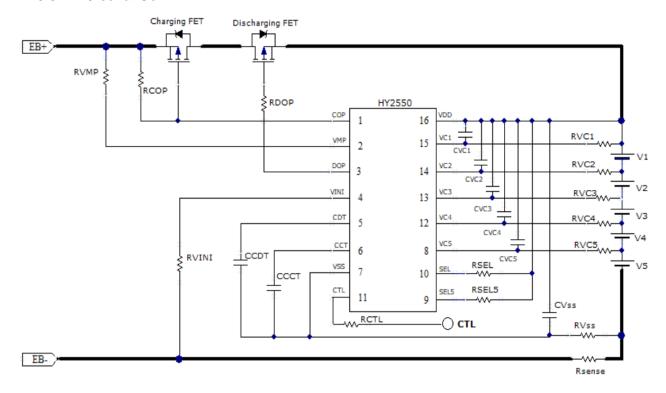

## 10. Example of Application Circuit for Battery Protection IC

#### 10.1 3-serial Cell

#### 10.2 4-serial Cell

## Protection IC for 3/4/5-Cell Li+ Battery

#### 10.3 5-serial Cell

## Protection IC for 3/4/5-Cell Li+ Battery

#### 10.4 Parts List

| Symbol            | Min. | Тур. | Max. | Unit | Remark |

|-------------------|------|------|------|------|--------|

| Rvc1              | 0    | 1    | 1    | kΩ   |        |

| Rvc2              | 0    | 1    | 1    | kΩ   |        |

| Rvcз              | 0    | 1    | 1    | kΩ   |        |

| Rvc4              | 0    | 1    | 1    | kΩ   |        |

| Rvc5              | 0    | 1    | 1    | kΩ   |        |

| RDOP              | 2    | 5.1  | 10   | kΩ   |        |

| Rcop              | 0.1  | 1    | 1    | ΜΩ   |        |

| RVMP              | 1    | 5.1  | 10   | kΩ   |        |

| RстL              | 1    | 1    | 100  | kΩ   |        |

| RVINI             | 1    | 1    | 100  | kΩ   |        |

| Rsel              | 1    | 1    | 100  | kΩ   |        |

| R <sub>SEL5</sub> | 1    | 1    | 100  | kΩ   |        |

| Rsense            | 0    | -    | -    | mΩ   |        |

| Rvss              | 10   | 51   | 51   | Ω    |        |

| C <sub>VC1</sub>  | 0    | 0.1  | 0.33 | μF   |        |

| Cvc2              | 0    | 0.1  | 0.33 | μF   |        |

| Сусз              | 0    | 0.1  | 0.33 | μF   |        |

| C <sub>VC4</sub>  | 0    | 0.1  | 0.33 | μF   |        |

| C <sub>VC5</sub>  | 0    | 0.1  | 0.33 | μF   |        |

| Ссст              | 0.01 | 0.1  | -    | μF   |        |

| Ссрт              | 0.07 | 0.1  | -    | μF   |        |

| Cvss              | 2.2  | 2.2  | 10   | μF   |        |

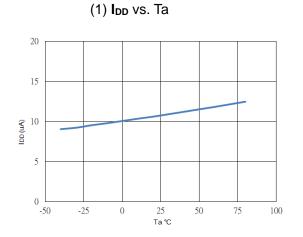

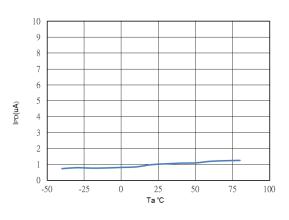

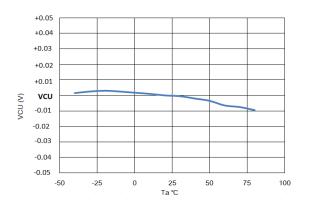

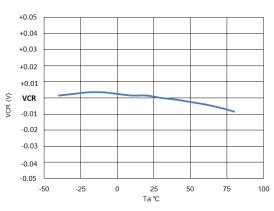

## 11. Temperature Characteristics (Typical Value)

(2) I<sub>PD</sub> vs. Ta

(3) Vcu vs. Ta

(4) VCR vs. Ta

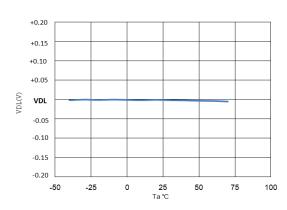

(5) V<sub>DL</sub> vs. Ta

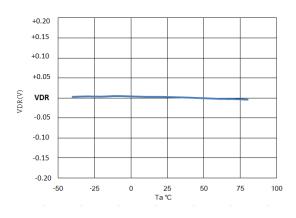

(6) V<sub>DR</sub> vs. Ta

## Protection IC for 3/4/5-Cell Li+ Battery

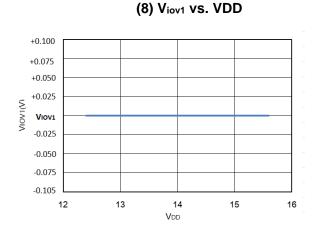

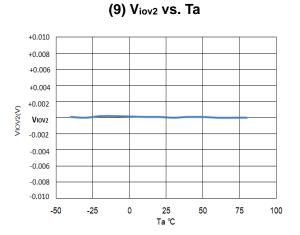

(7)Viov1 vs. Ta +0.100 +0.075 +0.050 +0.025 VIOV1 -0.025 -0.050 -0.075 -0.100 -25 25 50 75 100 Ta ℃

## Protection IC for 3/4/5-Cell Li+ Battery

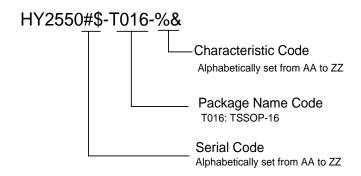

## 12. Ordering Information

Definition of Product Name

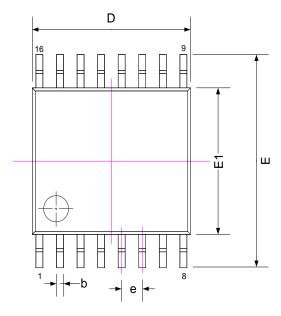

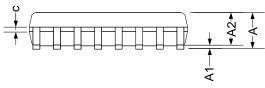

## 13. Package Information

Package Outline Drawing--- TSSOP16

| SYMBOLS | MIN       | NOM       | MAX  |  |  |

|---------|-----------|-----------|------|--|--|

| А       | -         | -         | 1.20 |  |  |

| A1      | 0.00      | -         | 0.15 |  |  |

| A2      | 0.80      | 1.00      | 1.05 |  |  |

| b       | 0.19      | -         | 0.30 |  |  |

| С       | 0.09      | -         | 0.20 |  |  |

| D       | 4.90      | 5.00      | 5.10 |  |  |

| E1      | 4.30      | 4.40      | 4.50 |  |  |

| Е       |           | 6.40 BSC. |      |  |  |

| L       | 0.45      | 0.60      | 0.75 |  |  |

| L1      | 1.0 REF.  |           |      |  |  |

| е       | 0.65 BSC. |           |      |  |  |

| θ°      | 0         | -         | 8    |  |  |

#### Note:

- 1. All dimensions refer to JEDEC OUTLINE MO -153.

- 2. Do not include Mold Flash or Protrusions.

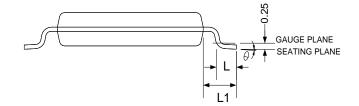

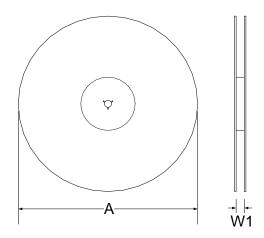

## 14. Tape & Reel Information

**Reel Dimensions**

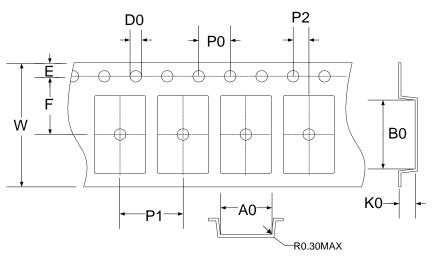

#### **Carrier Tape Dimensions**

| SYMBOLS   |       | eel<br>nsions |       |       | Ca    | arrier Ta | ape Dir | nensior | าร    |       |             |       |

|-----------|-------|---------------|-------|-------|-------|-----------|---------|---------|-------|-------|-------------|-------|

|           | Α     | W1            | A0    | В0    | K0    | P0        | P1      | P2      | Е     | F     | D0          | W     |

| Spec.     | 330   | 12.5          | 6.80  | 5.40  | 1.50  | 4.00      | 8.00    | 2.00    | 1.75  | 5.50  | 1.50        | 12.00 |

| Tolerance | +6/-3 | +1.5/-0       | ±0.10 | ±0.10 | ±0.10 | ±0.10     | ±0.10   | ±0.05   | ±0.10 | ±0.05 | +0.1/-<br>0 | ±0.30 |

#### Pin1 direction

## HY2550 Series Protection IC for 3/4/5-Cell Li+ Battery

#### 15. Revision Record

The larger modifications of this document are described below, but changes of punctuation marks and fonts are not within the scope of description.

## Version Page Summary of Modification

V01 - First release.