# HY16F3981 User's Guide

High-Precision Mixed Signal Micro Controller

4x32 ~ 6x30 LCD Driver

32-bit Low Power Micro Controller

21-bit ENOB ΣΔΑDC

64KB Flash ROM

## **Table of Contents**

| 1.   | CHIP OVERVIEW                      | 9  |

|------|------------------------------------|----|

| 1.1. | Brief introduction                 | 9  |

| 1.2. | Type description table             | 11 |

| 2.   | FUNCTION OVERVIEW                  | 12 |

| 2.1. | Block diagram                      | 12 |

| 2.2. | CPU core block diagram             | 13 |

| 3.   | MEMORY STRUCTURE                   | 14 |

| 3.1. | Memory description                 | 14 |

| 3.2. | Memory address                     | 15 |

| 3.3. | Static random-access memory (SRAM) | 16 |

| 3.4. | Flash ROM                          | 16 |

| 3.5. | Bus interface unit                 | 16 |

| 3.6. | Boot ROM                           | 17 |

| 3.7. | Embedded debug module (EDM)        | 17 |

| 4.   | SOC REGISTER                       | 18 |

| 4.1. | Overall description                | 18 |

| 4.2. | Register address                   | 18 |

| 4.3. | Register function                  | 18 |

| 5.   | POWER MANAGEMENT                   | 20 |

| 5.1. | Overall description                | 20 |

| 5.2. | Register address                   | 24 |

| 5.3. | Register function                  | 24 |

| 6.    | CLOCK SYSTEM             | 26 |

|-------|--------------------------|----|

| 6.1.  | Overall description      | 26 |

| 6.2.  | Register address         | 31 |

| 6.3.  | Register function        | 32 |

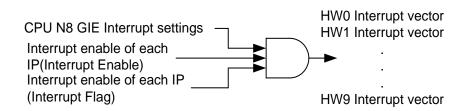

| 7.    | INTERRUPT CONTROL SYSTEM | 40 |

| 7.1.  | Overall description      | 40 |

| 7.2.  | Register address         | 41 |

| 7.3.  | Register function        | 42 |

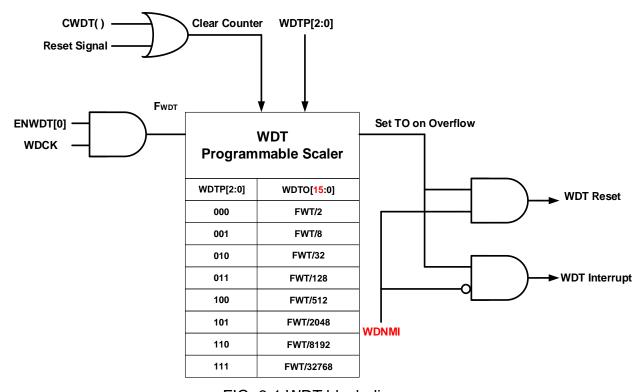

| 8.    | WATCH DOG TIMER (WDT)    | 53 |

| 8.1.  | Overall description      | 53 |

| 8.2.  | Register address         | 54 |

| 8.3.  | Register function        | 55 |

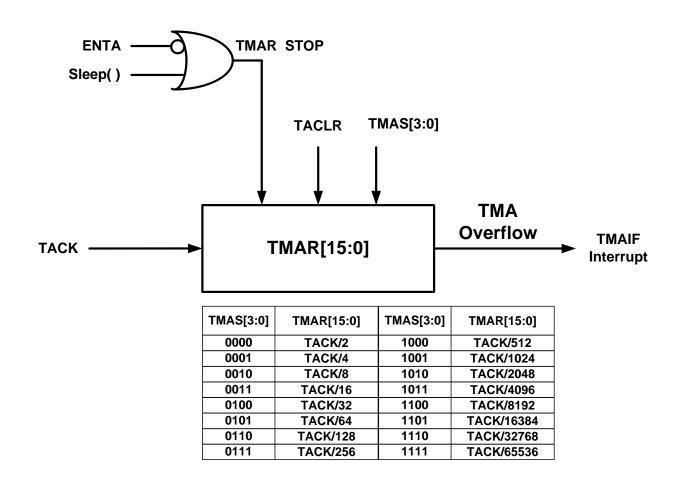

| 9.    | TIMER A                  | 56 |

| 9.1.  | Overall description      | 56 |

| 9.2.  | Register address         | 57 |

| 9.3.  | Register function        | 58 |

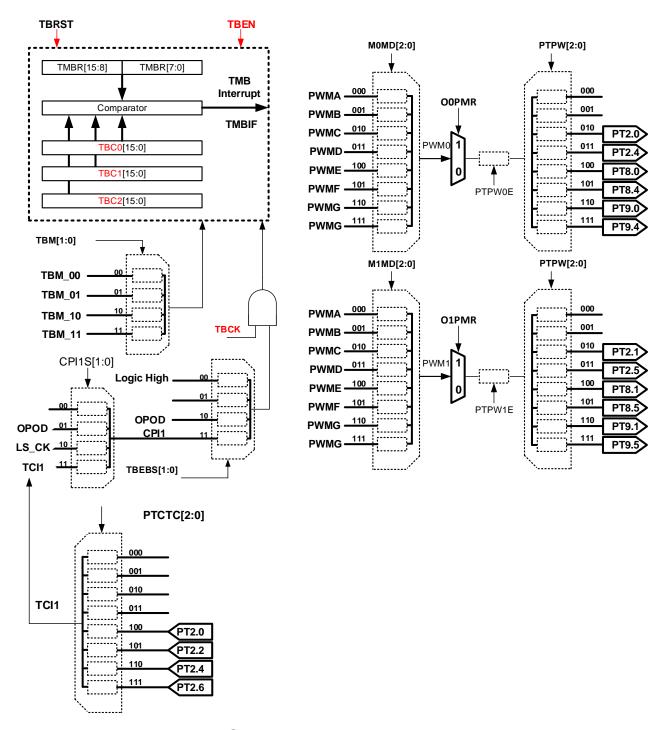

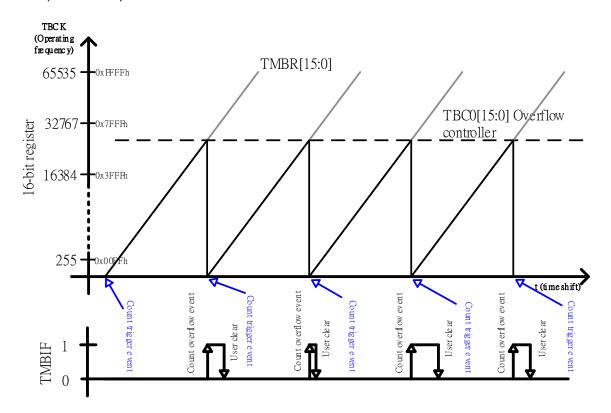

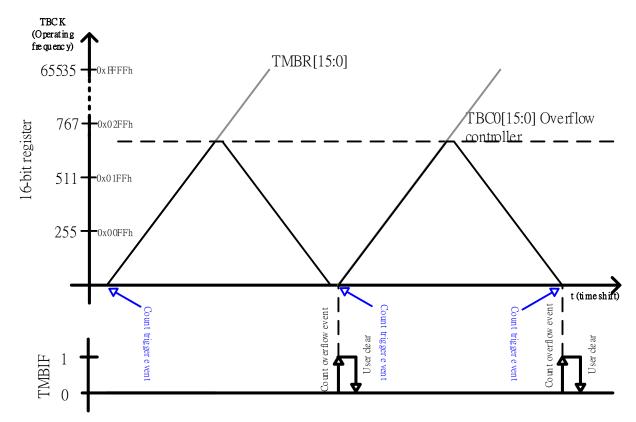

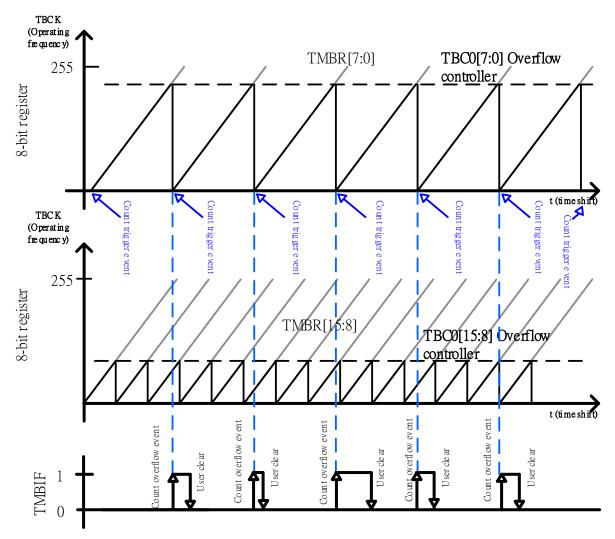

| 10.   | TIMER B                  | 59 |

| 10.1. | Overall description      | 59 |

| 10.2. | 2. Register address      | 85 |

| 10.3. | 3. Register function     | 85 |

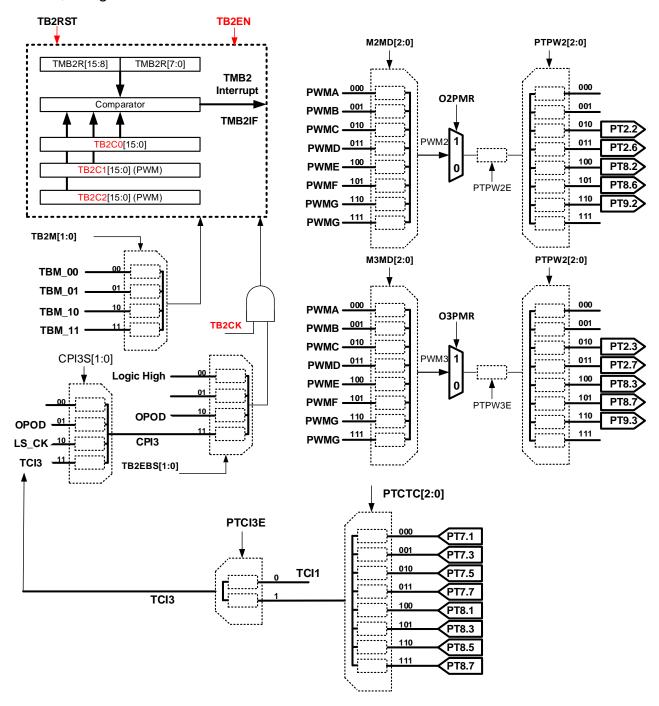

| 11.   | TIMER B2                 | 89 |

| 11.1. | . General description    | 89 |

| 11.2. | 2. Register address      | 90 |

| 11.3. | Register function                                                 | 90  |

|-------|-------------------------------------------------------------------|-----|

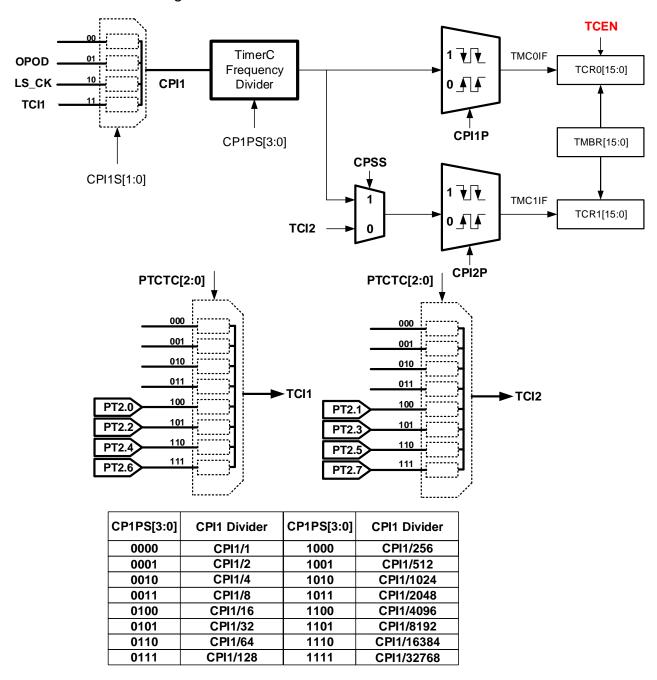

| 12.   | TIMER C                                                           | 94  |

| 12.1. | Overall description                                               | 94  |

| 12.2. | Register address                                                  | 97  |

| 12.3. | Register function                                                 | 97  |

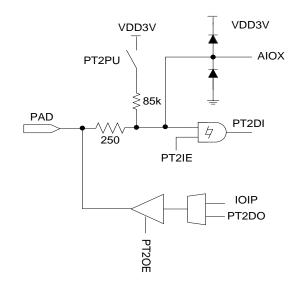

| 13.   | GPIO PT2 MANAGEMENT                                               | 100 |

| 13.1. | Overall description                                               | 100 |

| 13.2. | Register address                                                  | 102 |

| 13.3. | Register function                                                 | 102 |

| 13.4. | Analog to digital multiplexing function Switchover Considerations | 105 |

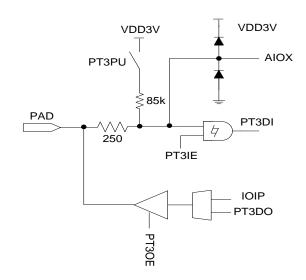

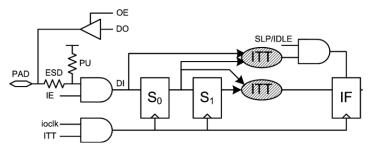

| 14.   | GPIO PT3 MANAGEMENT                                               | 106 |

| 14.1. | Overall description                                               | 106 |

| 14.2. | Register address                                                  | 108 |

| 14.3. | Register function                                                 | 109 |

| 14.4. | Analog to digital multiplexing function Switchover Considerations | 112 |

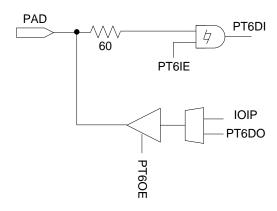

| 15.   | GPIO PT6 MANAGEMENT                                               | 113 |

| 15.1. | Overall description                                               | 113 |

| 15.2. | Register address                                                  | 115 |

| 15.3. | Register function                                                 | 115 |

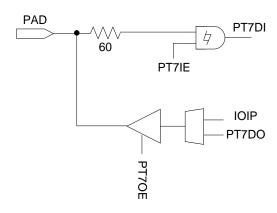

| 16.   | GPIO PT7 MANAGEMENT                                               | 122 |

| 16.1. | Overall description                                               | 122 |

| 16.2. | Register address                                                  | 123 |

| 16.3. | Register function                                                 | 123 |

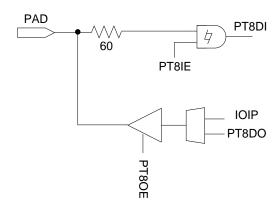

| 17.   | GPIO PT8 MANAGEMENT            | 130 |

|-------|--------------------------------|-----|

| 17.1. | . Overall description          | 130 |

| 17.2. | Register address               | 132 |

| 17.3. | 8. Register function           | 132 |

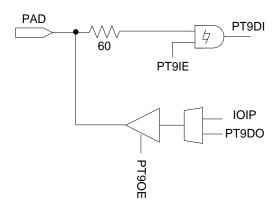

| 18.   | GPIO PT9 MANAGEMENT            | 140 |

| 18.1. | . Overall description          | 140 |

| 18.2. | Register address               | 142 |

| 18.3. | 8. Register function           | 142 |

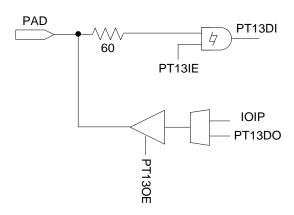

| 19.   | GPIO PT13 MANAGEMENT           | 148 |

| 19.1. | . Overall description          | 148 |

| 19.2. | Register address               | 149 |

| 19.3. | 8. Register function           | 149 |

| 20.   | GPIO MANAGEMENT                | 152 |

| 20.1. | . Overall description          | 152 |

| 20.2. | Register address               | 154 |

| 20.3. | 8. Register function           | 154 |

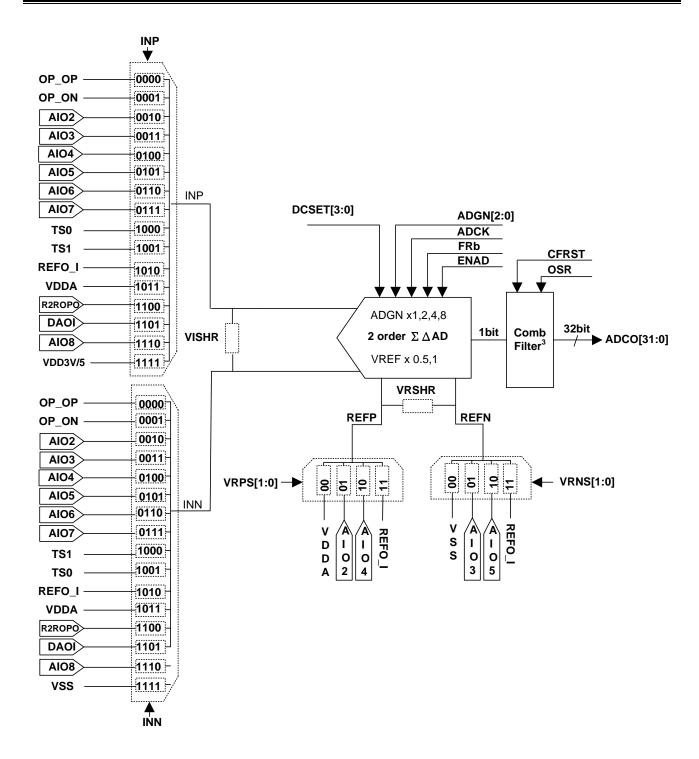

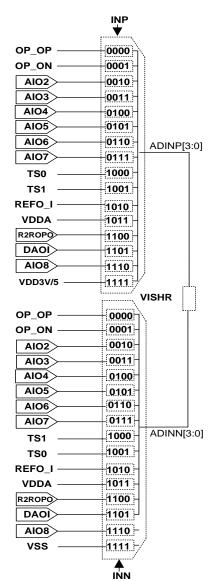

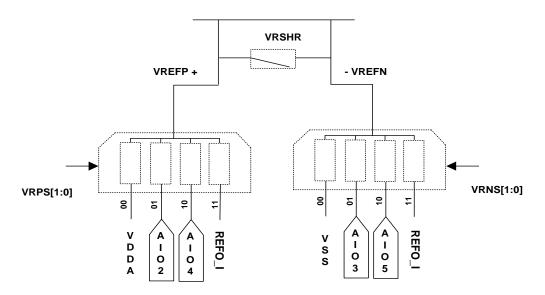

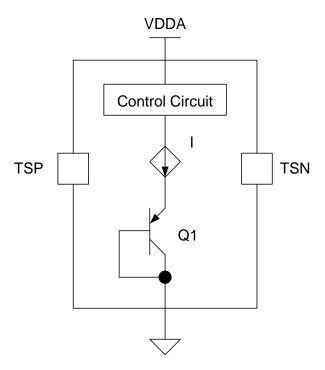

| 21.   | ΣΔ 24-BIT A/D CONVERTER (ADC)  | 159 |

| 21.1. | . Overall description          | 159 |

| 21.2. | Register address               | 170 |

| 21.3. | 8. Register function           | 170 |

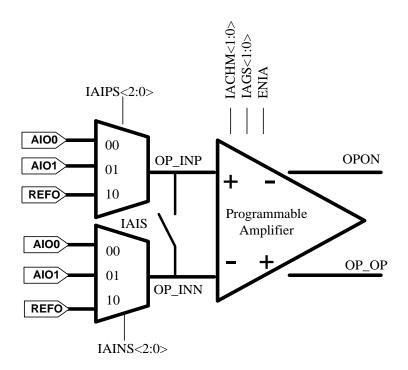

| 22.   | INSTRUMENTATION AMPLIFIER (IA) | 175 |

| 22.1. | . Overall description          | 175 |

| 22.2. | Register address               | 175 |

| 22.3. | Register function                                          | 175 |

|-------|------------------------------------------------------------|-----|

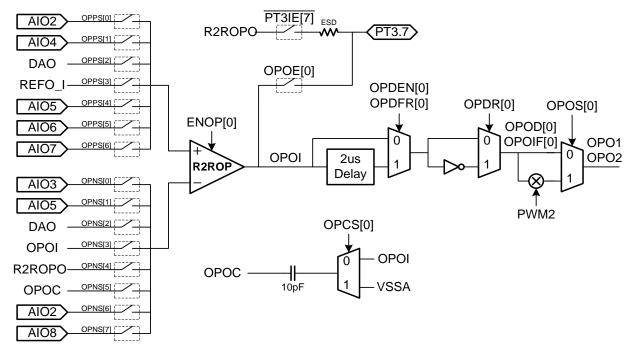

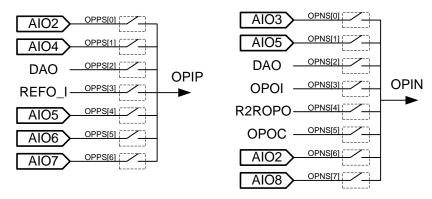

| 23.   | RAIL-TO-RAIL OPAMP                                         | 177 |

| 23.1. | Overall description                                        | 177 |

| 23.2. | Register address                                           | 181 |

| 23.3. | Register function                                          | 181 |

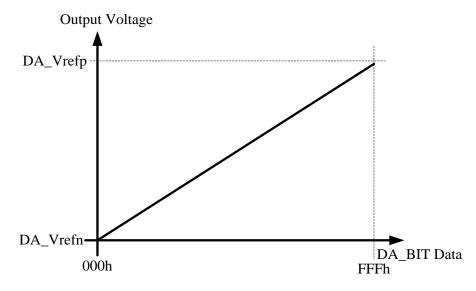

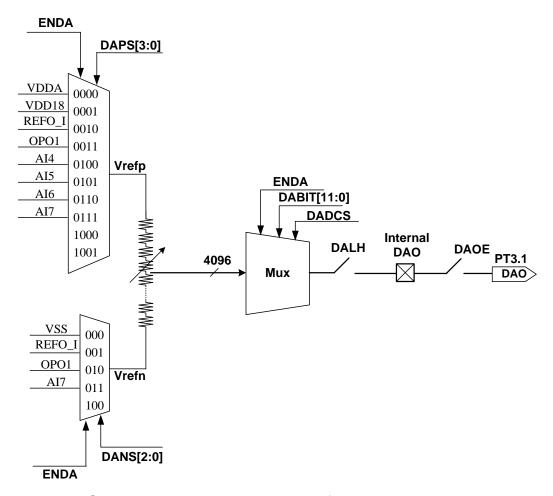

| 24.   | 12-BIT RESISTANCE LADDER NETWORK                           | 185 |

| 24.1. | Overall description                                        | 185 |

| 24.2. | Register address                                           | 187 |

| 24.3. | Register function                                          | 187 |

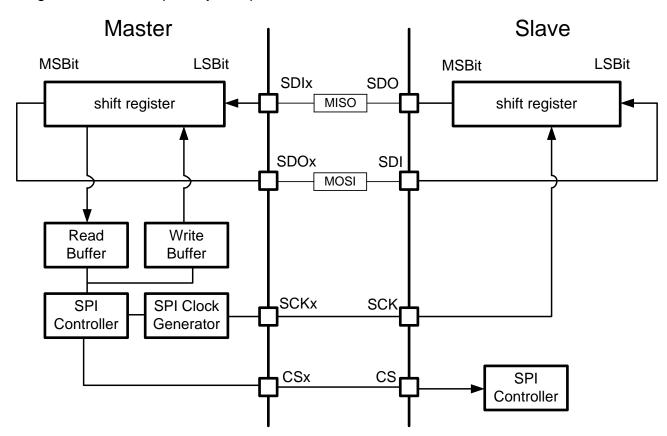

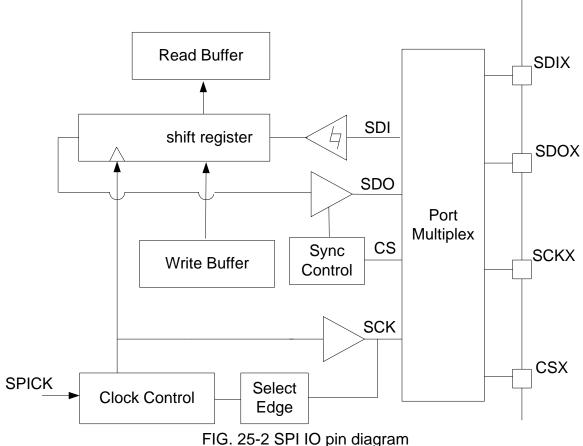

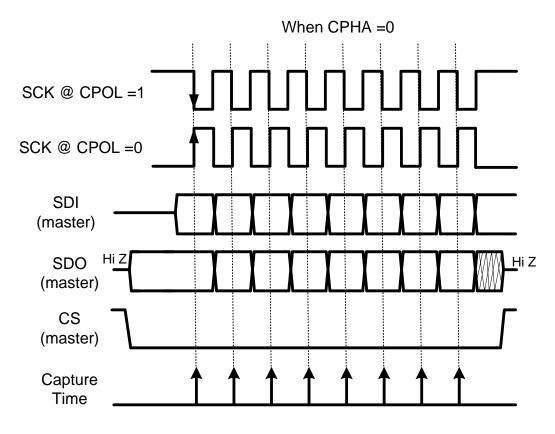

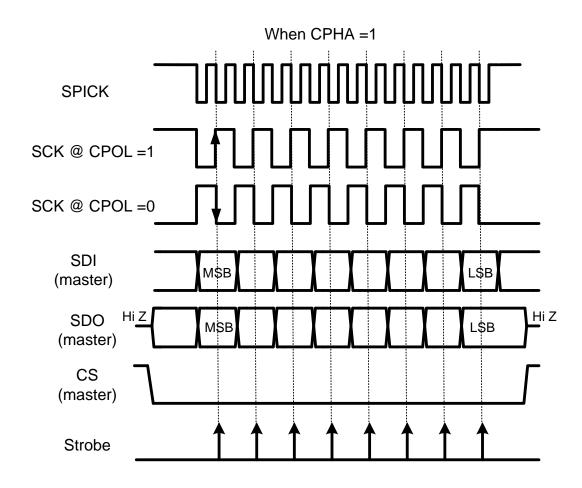

| 25.   | SERIAL PERIPHERAL INTERFACE (SPI)                          | 189 |

| 25.1. | Overall description                                        | 189 |

| 25.2. | Register address                                           | 194 |

| 25.3. | Register function                                          | 195 |

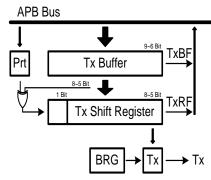

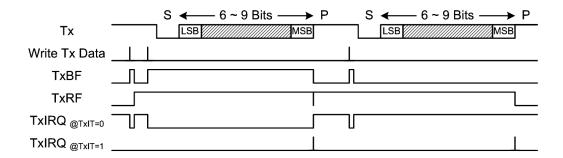

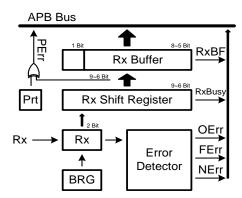

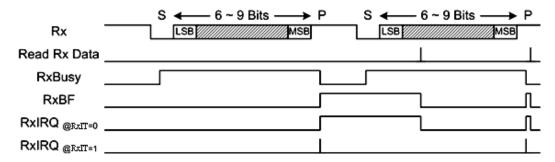

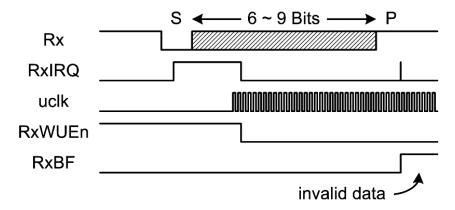

| 26.   | ENHANCED UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMIT (EUART)  | 200 |

| 26.1. | Overall description                                        | 200 |

| 26.2. | Register address                                           | 202 |

| 26.3. | Register function                                          | 203 |

| 26.4. | UART using instruction:                                    | 206 |

| 27.   | ENHANCED UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMIT (EUART2) | 210 |

| 27.1. | Overall description                                        | 210 |

| 27.2. | Register address                                           | 210 |

| 27.3. | Register function                                          | 210 |

| 27.4. | UART2 using instruction.                                   | 213 |

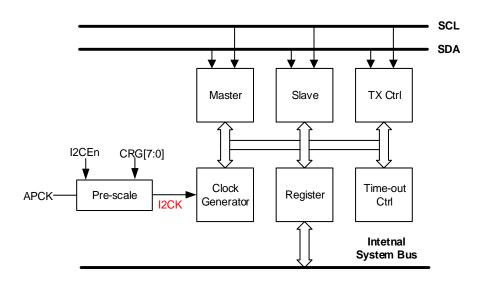

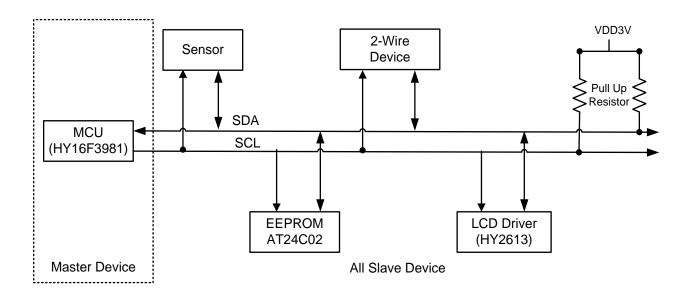

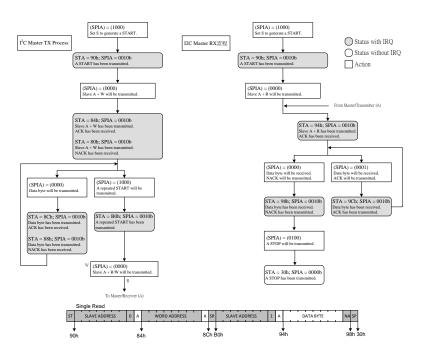

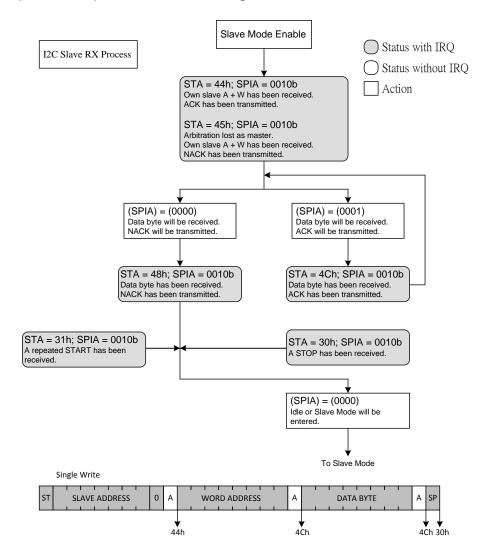

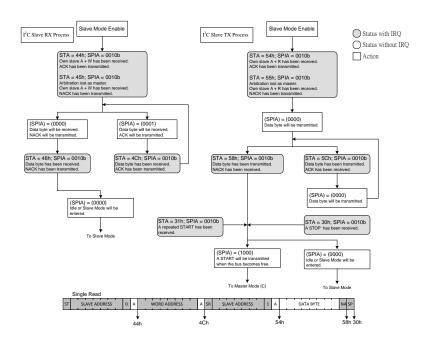

| 28.   | I2C COMMUNICATION INTERFACE        | 214 |

|-------|------------------------------------|-----|

| 28.1. | Overall description                | 214 |

| 28.2. | Register address                   | 224 |

| 28.3. | Register function                  | 224 |

| 28.4. | Model program function             | 231 |

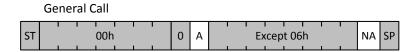

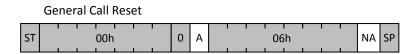

| 28.5. | I <sup>2</sup> C General Call Mode | 242 |

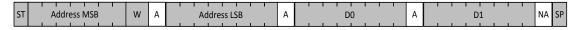

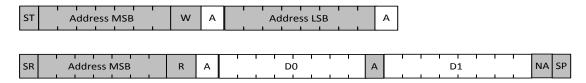

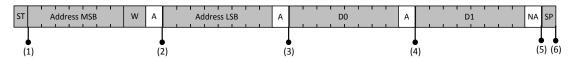

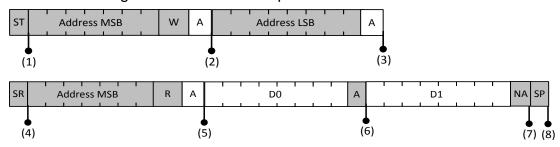

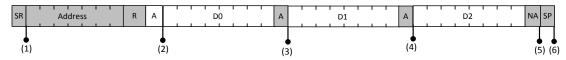

| 28.6. | 10 Bit Addressing Mode             | 243 |

| 28.7. | 3 Byte Data Mode                   | 247 |

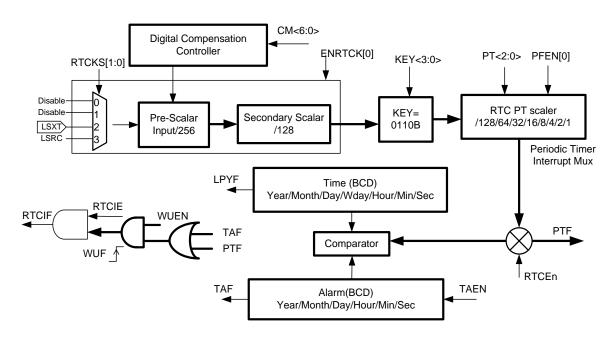

| 29.   | HARDWARE REAL TIME CLOCK (HW RTC)  | 249 |

| 29.1. | Overall description                | 249 |

| 29.2. | Register address                   | 251 |

| 29.3. | Register function                  | 252 |

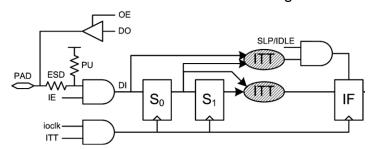

| 30.   | POWER-SAVING MODE INTRODUCTION     | 265 |

| 30.1. | Overall description                | 265 |

| 30.2. | Interrupt point configuration      | 265 |

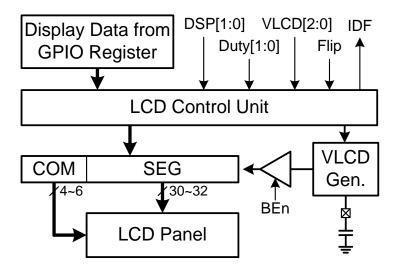

| 31.   | LCD DRIVER                         | 268 |

| 31.1. | Overall description                | 268 |

| 31.2. | Register address                   | 269 |

| 31.3. | Register function                  | 270 |

| 31.4. | LCD RAM function                   | 275 |

| 31.5. | LCD power saving features          | 275 |

| 32.   | REVISIONS                          | 276 |

#### Attention:

- 1 > HYCON Technology Corp. reserves the right to change the content of this datasheet without further notice. For most up-to-date information, please constantly visit our website: http://www.hycontek.com.

- 2 HYCON Technology Corp. is not responsible for problems caused by figures or application circuits narrated herein whose related industrial properties belong to third parties.

- 3 Specifications of any HYCON Technology Corp. products detailed or contained herein stipulate the performance, characteristics, and functions of the specified products in the independent state. We does not guarantee of the performance, characteristics, and functions of the specified products as placed in the customer's products or equipment. Constant and sufficient verification and evaluation is highly advised.

- 4 Please note the operating conditions of input voltage, output voltage and load current and ensure the IC internal power consumption does not exceed that of package tolerance. HYCON Technology Corp. assumes no responsibility for equipment failures that resulted from using products at values that exceed, even momentarily, rated values listed in products specifications of HYCON products specified herein.

- 5 Notwithstanding this product has built-in ESD protection circuit, please do not exert excessive static electricity to protection circuit.

- 6 Products specified or contained herein cannot be employed in applications which require extremely high levels of reliability, such as device or equipment affecting the human body, health/medical equipments, security systems, or any apparatus installed in aircrafts and other vehicles.

- 7 Despite the fact that HYCON Technology Corp. endeavors to enhance product quality as well as reliability in every possible way, failure or malfunction of semiconductor products may happen. Hence, users are strongly recommended to comply with safety design including redundancy and fire-precaution equipments to prevent any accidents and fires that may follow.

- 8 \ Use of the information described herein for other purposes and/or reproduction or copying without the permission of HYCON Technology Corp. is strictly prohibited.

#### 1. CHIP OVERVIEW

#### 1.1. Brief introduction

The HY16F3981 is a low-power and high-precision mixed signal micro controller (MCU) with LCD driver (Liquid Crystal Display), and is applicable to perform high-precision measurement and control; besides, the controller can work in a wide voltage range (2.2V-3.6V) and the clock of the controller can be up to 16MHz; further, the controller has a built-in 64kbyte embedded Flash ROM and a 8kbyte SRAM. The HY16F3981 products integrate a high-precision 24-bit ΣΔ A/D converter, Rail-to-Rail OPAMP, 12-bit Resistance Ladder, Hardware RTC; moreover, the HY16F3981 products provide high-performance peripheral interfaces, such as the UART, SPI, I2C, GPIO and built-in power management system, etc., and support low-voltage detection and multiple peripheral interface wake-up functions. The HY16F3981 products are of low voltage, low power, low stand-by current, high integrity and high efficient operation, and support the 32-bit micro controller of the C development platform. Therefore, the HY16F3981 products can provide various resources for designers to design a low-current and low-cost mixed signal processing system.

The analog front-end circuit controller includes a 12-bit resistance ladder, a Rail-to-Rail OPAMP. In particular, 12-bit resistance ladder has monotonicity, which is a step resistor, and the least significant bit (LSB) is close to 200 ohm and the resistor has the low-temperature coefficient. The Rail-to-Rail OPAMP has an input network, which is applicable for the differential analog circuit configuration, such as integrator, current-to-voltage converter, programmable gain amplifier and successive approximation A/D converter.

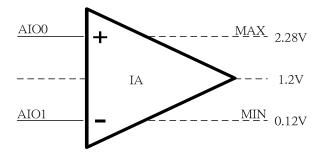

The 24 bits A/D converter with extremely low noise is embedded. Its maximal output rate is 15KSPS, its ENOB (Effective number of bit) is 21, and its minimal resolvable signal is 1.1uV RMS Noise (Root- Mean- Square). ADC front-end built-in instrumentation amplifier IA, Maximum input magnification up to 256x magnification.

The power management provides selectable analogous regulating voltage, which can serve as reference voltage source or the power supply of a transducer. The working power source of the CPU is also provided by the internal linear stabilized power supply. 64Kbyte embedded Flash ROM can be used to execute programs or store data; the data can be still stored into the Flash ROM even if the Flash ROM is executing a program. A built-in 8kbyte SRAM is provided for the system to use.

The core of the 32-bit high-performance mixed signal micro controller can execute an instruction during each clock cycle, which can be up to 16MIPS (Millions of Instructions per Second) and conform to low power consumption indicator. HYCON Technology provides convenient programming tools for users to write programs by C/C++ language or assembly language in the development platform. The chip has the circuit simulation function and provides a good environment for troubleshooting. The chip can work in 2.2V to 3.6V and -40°C to 85°C.

# 1.2. Type description table

The bit type description table of the register

| Setting<br>type | Description Description | Initial value          |

|-----------------|-------------------------|------------------------|

| -               | No Use                  |                        |

| RSV.            | Reserve                 |                        |

| X               | Unknown                 |                        |

| W               | Write                   |                        |

| R               | Read                    |                        |

| R0              | Only Read 0             |                        |

| R1              | Only Read 1             |                        |

| W0              | Only Write 0            |                        |

| W1              | Only Write 0            |                        |

| RW-0            | Read/ Write             | Initial 0              |

| RW-1            | Read/ Write             | Initial 1              |

| R0W-0           | Read 0/ Write           | Initial 0              |

| R1W-1           | Read 1/ Write           | Initial 1              |

| R-X             | Read                    | Initial 1 or 0 Unknown |

| []              | Register length         |                        |

| <>              | Register value          |                        |

| ABC[7:0]        | ABC register had 0      |                        |

|                 | to 7bit                 |                        |

| ABC<111>        | ABC register had        |                        |

|                 | 3bit and value had      |                        |

|                 | 111 of binary           |                        |

| ABC<11x>        | x : can be              |                        |

|                 | neglected, it can be    |                        |

|                 | set as 1 or 0           |                        |

#### 2. FUNCTION OVERVIEW

## 2.1. Block diagram

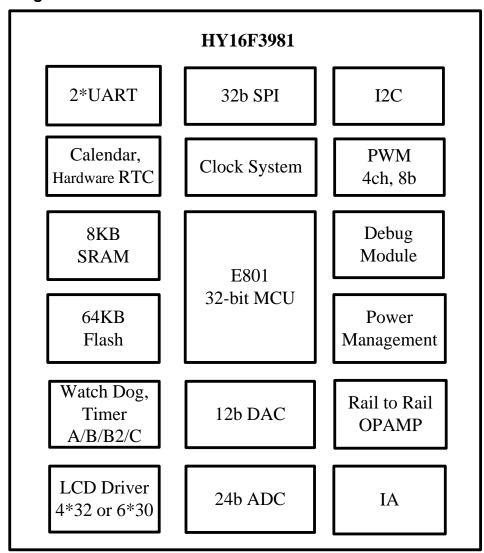

FIG. 2-1 Chip function structure diagram

## 2.2. CPU core block diagram

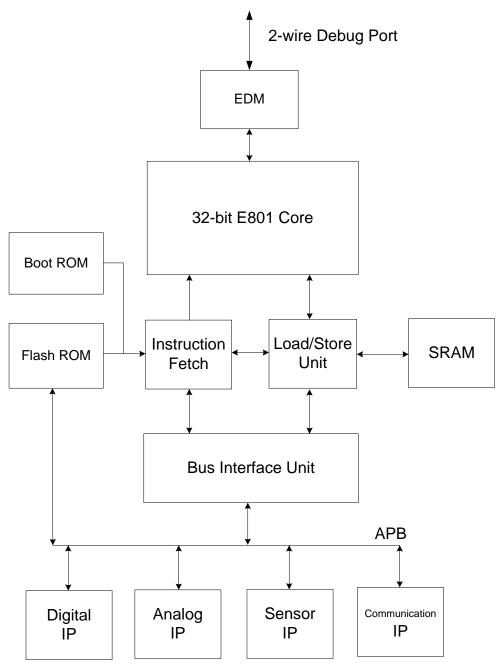

FIG. 2-2 CPU core block diagram

#### 3. MEMORY STRUCTURE

## 3.1. Memory description

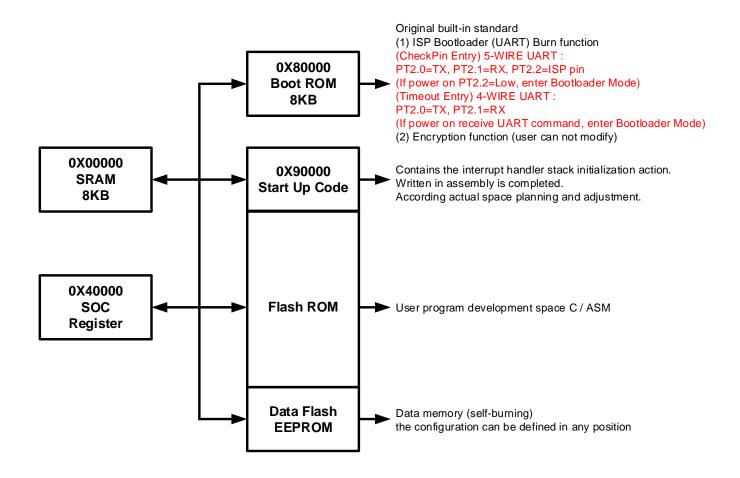

The core of the CPU (Central Processing Unit) of HY16F3981 series products is Andes 32-bit CPU. The allocation of the memory addresses of the micro controller is as follows:

0x00000 to 0x01FFF Static random-access memory (SRAM) (8K Byte)

0x40000 to 0x4FFFF SOC Register

0x80000 to 0x81FFF Boot ROM (8K Byte): Support (Timeout Entry)4-WIRE and (CheckPin Entry) 5-WIRE UART interface ROM ISP Bootloader function. The default setting is DISABLE status. User can use HY16F Writer(Or IC programming service) to ENABLE ROM ISP Bootloader function.

0x90000 to 0x9FFFF Main Program Flash ROM (64K Byte)

FIG. 3-1 Memory address allocation diagram

#### 3.2. Memory address

The detailed address allocation of the SOC registers of the micro controller is as follows:

| Function module | Description                                | Base Address |

|-----------------|--------------------------------------------|--------------|

| INT             | Interrupt control Flag                     | 0x40000      |

| SoC             | System control register                    | 0x40100      |

| CLK             | Clock system control register              | 0x40300      |

| PMU             | Power management control register          | 0x40400      |

| MC              | Memory controller register                 | 0x40600      |

| PIO             | GPIO port control register                 | 0x40800      |

| TMR             | Timer register                             | 0x40C00      |

| UART            | UART mode control register                 | 0x40E00      |

| SPI             | SPI mode control register                  | 0x40F00      |

| I2C             | I2C mode control register                  | 0x41000      |

| ADC             | Analog-to-Digital module control register  | 0x41100      |

| IA              | instrumentation amplifier control register | 0x41600      |

| 12-bit          |                                            |              |

| resistance      | Resistance Ladder Module control register  | 0x41700      |

| ladder          |                                            |              |

| R2R OPAMP       | R2R Operational amplifier control register | 0x41900      |

| RTC             | Real time clock control register           | 0x41A00      |

| LCD             | LCD driver control register                | 0x41B00      |

Table 3-1 SOC registers

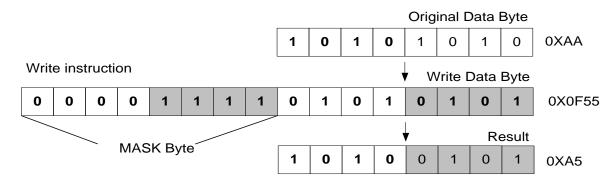

Some important registers have MASK bits, as describe in FIG. 3-3. MASK is used to control written-in bits; only when the MASK bit corresponding to the control bit is <1>, the corresponding control bit can be written in, or the written-in operation will be invalid and cannot actually modify the value of the register, as shown in FIG. 3-2.

The total length of a register is 32-bit and most registers have 16 MASK bits. The MASK bits include two 8-bit groups, and each 8-bit group controls corresponding 8 control register bits. According to the content allocation of a register: BIT [31:24] controls BIT [23:16], and BIT [15:8] controls BIT [7:0]. Only when the MASK bit is <1>, the corresponding control bit can be validly written in.

For example, if a user wants to write 101010b in BIT [5:0] and the write value of the register should be: 0011111100101010b, where 00111111b are the MASK bits of BIT [5:0] and can make written-in corresponding control bits valid; and 00101010b are the values written in BIT [5:0].

|        | INT Base Address + 0x10 (0x40010) |                                             |                                                         |        |        |        |        |        |        |

|--------|-----------------------------------|---------------------------------------------|---------------------------------------------------------|--------|--------|--------|--------|--------|--------|

| Symbol |                                   | INTPT1 (PT1 Interrupt Control Register)     |                                                         |        |        |        |        |        |        |

| Bit    | [31:24]                           | 24] [23] [22] [21] [20] [19] [18] [17] [16] |                                                         |        |        |        |        |        | [16]   |

| Name   | MASK                              | PT17IE                                      | PT17IE PT16IE PT15IE PT14IE PT13IE PT12IE PT11IE PT10II |        |        |        |        |        | PT10IE |

| RW     | R0W-0                             |                                             |                                                         |        | RV     | V-0    |        |        |        |

| Bit    | [15:08]                           | [7]                                         | [7] [6] [5] [4] [3] [2] [1] [0]                         |        |        |        |        |        |        |

| Name   | MASK                              | PT17IF                                      | PT16IF                                                  | PT15IF | PT14IF | PT13IF | PT12IF | PT11IF | PT10IF |

| RW     | R0W-0                             | RW0-0                                       |                                                         |        |        |        |        |        |        |

FIG. 3-2 Basic structure of register

#### 3.3. Static random-access memory (SRAM)

HY16F3981 has an 8Kbyte SRAM. The initial address is from 0x00000 to 0x01FFF. MCU can select to access one byte, half word or one word. MCU can access one word during each clock cycle.

## 3.4. Flash ROM

HY16F3981 has a 64Kbyte embedded Flash ROM. The initial value is from 0x90000 to 0x9FFFF. User programmable codes are stored in the Flash ROM. A user needs to use CPU instructions to read and write the Flash ROM if wanting to edit the program codes of the Flash ROM. The user can store data at any positions between the blocks.

#### 3.5. Bus interface unit

Regarding the structure of a bus, the reading and writing of the register are controlled by a 32-bit advanced peripheral bus (APB), which can write in 32-bit data during each clock cycle. In order to prevent from the existing data be covered when writing in new data, the user can use the MASK function to finish the operation.

As described in FIG. 3.3, the original data in BIT[7:0] of the register are 10101010b, and the written-in data are made valid via the MASK bits; when 0000111101010101b are written in BIT[15:0], the result will be 000000001010010b, which means the MASK bit can only be set as 1b and the read value will be 0b; when 0101b are written in BIT[7:4], but the definition of BIT[15:12] is 0000b; therefore, it means the write values of BIT[7:4] are invalid; when 0101b are written in BIT[3:0] and the definition of MASK BIT[11:8] is 1111b; therefore, it means the write values of BIT[3:0] can be valid.

FIG. 3-3 Data flow structure

#### 3.6. Boot ROM

8Kbyte Boot ROM is provided, and the initial value is from 0x80000 to 0x81FFF. The blocks are for boot codes, flash codes and security codes. When the chip is reset, the program timer will start from 0x80000. The software of the Boot ROM includes much information, such as system program protocol, security protocol and the like.

#### 3.7. Embedded debug module (EDM)

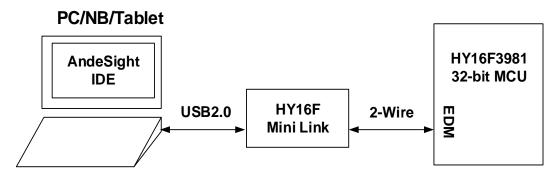

The embedded debug module (EDM) is a debug interface which can be used by the chip in the development environment. When the chip has no security protection, the user can transmit instructions to the MCU via EDM interface to read the information of the debug mode. EDM is the bridge of the communication between the chip and the computer The PC USB and the chip EDM are connected via HY16F Mini Link (USB control board) by only using a two-wire protocol interface. EDM can access the control register, general GPR register, SRAM DLM and Flash ROM ILM of a chip.

FIG. 3-4 Chip development connection diagram

#### 4. SOC REGISTER

#### 4.1. Overall description

Manage the operating mode of the system and the reset status of the chip, such as WDT, external reset, under voltage reset, etc.

## 4.2. Register address

| SoC Status Register Address             | 31 | 24 | 23 | 16 | 15  | 8   | 7  | 0  |

|-----------------------------------------|----|----|----|----|-----|-----|----|----|

| SoC Status Base Address + 0x04(0x40104) |    | -  |    | -  | MA: | SK0 | RE | G0 |

<sup>-</sup>Reserved

## 4.3. Register function

Operate the register SoC 0x40104 [4] can set the operating mode of the system as SLEEP mode/IDLE mode. The user can check the register SoC 0x40104[3] to understand what the current operating mode of the system is.

# 4.3.1. SOC register

|        | SoC Status Base Address + 0x04 (0x40104) |     |               |     |    |                          |                   |       |       |      |

|--------|------------------------------------------|-----|---------------|-----|----|--------------------------|-------------------|-------|-------|------|

| Symbol | SoC Status Register                      |     |               |     |    |                          |                   |       |       |      |

| Bit    | [31:24]                                  |     |               |     |    |                          | [23:16]           |       |       |      |

| Name   | ICE Configuration                        |     |               |     |    |                          | SoC Configuration |       |       |      |

| RW     | R-0x0F                                   |     |               |     |    |                          |                   | R-0x1 | С     |      |

| Bit    | [15:8]                                   | [7] | [6]           | [5] | [4 | 4]                       | [3]               | [2]   | [1]   | [0]  |

| Name   | MASK                                     | -   | FPRG FCRst ID |     |    | OLE FSLP/IDLE FWDog FRST |                   |       | Frst  | FBOR |

| RW     | R0W-0 - RW0-0                            |     |               |     |    |                          |                   |       | RW0-1 |      |

| Bit     | Name                  | Des                   | Description                                                |  |  |  |  |  |

|---------|-----------------------|-----------------------|------------------------------------------------------------|--|--|--|--|--|

|         |                       | Pow                   | er Good Flag                                               |  |  |  |  |  |

| Bit[06] | F <sub>PRG</sub>      | 0                     | Normal                                                     |  |  |  |  |  |

|         |                       | 1                     | Power Good has already been triggered before.              |  |  |  |  |  |

|         |                       | CPL                   | CPU Core Reset Flag                                        |  |  |  |  |  |

| Bit[05] | 5] FCRST              | 0                     | Normal                                                     |  |  |  |  |  |

|         |                       | 1                     | ICP Core has already been triggered before.                |  |  |  |  |  |

|         |                       | IDLE Mode Control Bit |                                                            |  |  |  |  |  |

| Bit[04] | IDLE                  | 0                     | Sleep Mode                                                 |  |  |  |  |  |

|         |                       | 1                     | IDLE Mode                                                  |  |  |  |  |  |

|         |                       | Slee                  | p/Idle Flag                                                |  |  |  |  |  |

| Bit[03] | F <sub>SLP/IDLE</sub> | (Low                  | v voltage reset or reset circuit reset can reset the bit.) |  |  |  |  |  |

|         |                       | 0                     | Normal                                                     |  |  |  |  |  |

|         |                  | 1    | Sleep Mode or Idle Mode                                               |  |  |  |  |

|---------|------------------|------|-----------------------------------------------------------------------|--|--|--|--|

|         |                  | WD   | T Flag (Low voltage reset or external reset can clear the bit.)       |  |  |  |  |

| Bit[02] | $F_{WDT}$        | 0    | Normal                                                                |  |  |  |  |

|         |                  | 1    | WDT is reset or interrupted.                                          |  |  |  |  |

|         |                  | Exte | ernal Reset Flag (Low voltage reset (BOR) can clear the bit.)         |  |  |  |  |

| Bit[01] | F <sub>RST</sub> | 0    | Normal                                                                |  |  |  |  |

|         |                  | 1    | Reset PIN or ICP software reset has occurred.                         |  |  |  |  |

|         |                  | Low  | Voltage Reset (BOR) Flag (The bit will be automatically cleared after |  |  |  |  |

| Dit[00] | E                | the  | voltage of the chip is higher than 1.8V.)                             |  |  |  |  |

| Bit[00] | F <sub>BOR</sub> | 0    | Normal                                                                |  |  |  |  |

|         |                  | 1    | Low voltage reset has occurred.                                       |  |  |  |  |

#### 5. POWER MANAGEMENT

#### 5.1. Overall description

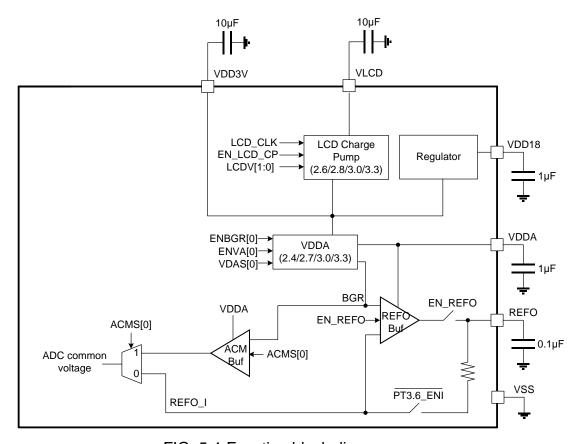

Power management module includes a charge pump regulator, a wide BandGap reference, a narrow BandGap reference, a VDDA LDO, a VDD18 LDO and a reference output buffer. Chip VDD3V can work by only one voltage source between 2.2V and 3.6V. The power system can be classified into three parts: I/O circuit, analog circuit, and digital circuit. The power supply of the I/O circuit is driven by VDD3V. The power supply of the analog circuit is driven by the internal VDDA LDO. Finally, the power supply of the digital circuit is driven by VDD18 LDO.

When the MCU is under IDLE mode, it will use lowest power consumption to perform the memory operation of the register and the SRAM. During the IDLE mode, the wide BandGap reference, BOR and VDD18 LDO are enabled. If the MCU is under the automatic wake-up mode, the low-speed oscillator should be enabled.

FIG. 5-1 Function block diagram

#### Chip operating voltages VDD3V and VDD18

The operating voltage of the chip is inputted via the pin VDD3V, and the voltage range is 2.2V~3.6V; besides, the pin should be connected to a 10uF ground capacitor, which can make VDD3V become more stable.

The VDD18 LDO output a stable voltage 1.8V via the VDD18 pin and the pin should be connected to a 1uF bypass capacitor.

#### VDDA voltage

The chip has a voltage regulator circuit LDO: VDDA and the VDDA voltage should be enabled when using ADC. It can have different operating modes and different output voltages. It has four different operating modes; the first mode is to be short-circuited to the VDD3V; and the VDDA is close to the VDD3V during the mode. The second mode is Weak pull down; during the mode, the VDDA is close to the VSS. The third mode is High Z; and it is possible to input the voltage into the VDDA from outside but the inputted voltage should not exceed VDD3V. The four modes is adjustable voltage regulating mode LDO; during the mode, the VDDA can output four different voltages: 2.4V, 2.7V, 3.0V and 3.3V. For better performance, the voltage difference between VDD3V and VDDA. Should be higher than 0.2V and can drive at most 10mA. Additionally, it also needs to be connected to a 1uF bypass capacitor. Note that when connecting a 1uF VDDA to-ground capacitance, stabilization time VDDA at least require more than 0.5ms, when VDDA access a 10uF capacitance to ground, settling time of at least VDDA greater than 1ms.

#### Low voltage detection circuit (BOR)

The BOR circuit is used to monitor the stability of the power system and the MCU. When the BOR detects the VDD3V and VDD18 are lower the detecting voltage of the BOR, the BOR will be triggered to reset the system and the chip; the chip will work normally until the BOR detects the operating voltage of the chip exceeds the voltage of the BOR.

#### Reference voltage and common mode voltage (REFO)

When the VDDA is higher than 2.4V, the analog circuit can work. However, the analog circuit needs the current offset and the reference voltage. Therefore, the BandGap reference voltage should be enabled before the analog circuit is enabled; the BandGap reference voltage can be enabled by setting the register PMU [4] (ENBGR) as 1. Only after the BandGap reference voltage is enabled, the common mode voltage (REFO) can effectively output 1.2V.

It is necessary to provide a common mode voltage (REFO) for the ADC to enable it. If the user wants to use the internal power supply, the ACMS should be set as 1; if the user wants to the external power supply, the ACMS should be set as 0 to output a common mode voltage (REFO). The user will need to use a reference voltage to drive the external

circuit; therefore, the ENRFO should be set as 1 to output the common mode voltage to the pin; besides, the REFO is the BandGap reference voltage with buffer. The output voltage of the REFO pin is about 1.2V and has +/-1mA push-pull driving ability. It can drive a 22~1000nF big capacitor load. If the external REFO voltage output is used, the common mode voltage for the ADC can be provided by an external power supply; in this case, the ACMS can be set as 0 to save more power. Note that when a 0.1uF REFO access to ground capacitance, REFO stabilization time at least more than 0.1ms.

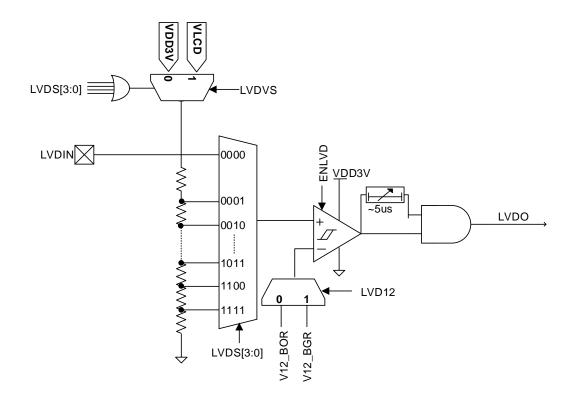

#### LVD low voltage detection:

Low voltage detection provides a settable low voltage detection function for operating voltage VDD3V, VLCD voltage external input voltage LVDIN. The LVD reference voltage source is selectable BOR or BGR(Band Gap reference voltage). When the input voltage is external voltage LVDIN, the low voltage detection point set LVDS must be set to 0000b, then the low voltage detection point is 1.2V, that is BOR or BGR actual voltage; when the input voltage is VDD3V or VLCD, the low voltage detection point LVDS setting range is 0001b~1111b (2.0V ~ 3.4V).

#### Setup process:

- (1) Select the input voltage, if the external voltage input (LVDIN) is not required to set the register, or through the LVDVS settings select VDD3V or VLCD.

- (2) Select the reference voltage and select V12\_BOR or V12\_BGR through the LVD12 setting.

- (3) Set the low voltage detection point. If select the external voltage input (LVDIN), LVDS is set to 0000b. If select the VDD3V or VLCD, set LVDS low voltage detection point 0001b~1111b (2.0V ~ 3.4V).

- (4) Enable low voltage comparator ENLVD, start low voltage detection.

The following table shows the voltage sources for all modules.

| Block name          | Voltage source | Block name               | Voltage |

|---------------------|----------------|--------------------------|---------|

|                     |                |                          | Source  |

| 32-bit CPU Core     | VDD18          | Timer A/B/C PWM          | VDD18   |

| 08KB SRAM           | VDD18          | GPIO Port                | VDD3V   |

| 64KB Flash ROM      | VDD3V/ VDD18   | 24-bit SD ADC            | VDDA    |

| Clock System        | VDD18          | 12-bit Resistance ladder | VDDA    |

| Watch Dog Timer     | VDD18          | Rail-to-Rail OPAMP       | VDDA    |

| Hardware RTC        | VDD18          |                          |         |

| BOR                 | VDD3V/ VDD18   |                          |         |

| Band Gap/Reference  | VDDA           |                          |         |

| Hardware EUART      | VDD18/VDD3V    |                          |         |

| 32-bit Hardware SPI | VDD18/VDD3V    |                          |         |

| Hardware I2C        | VDD18/VDD3V    |                          |         |

Table 5-1 Chip Power supply distribution

## 5.2. Register address

| Power Management Register Address | 31 | 24  | 23 | 16   | 15  | 8   | 7  | 0  |

|-----------------------------------|----|-----|----|------|-----|-----|----|----|

| PMU Base Address + 0x00 (0x40400) | MA | SK1 | R  | EG1  | MA: | SK0 | RE | G0 |

| PMU Base Address + 0x08 (0x40408) |    | Rsv |    | REG3 | MA: | SK0 | RE | G2 |

# 5.3. Register function

## **Power management registers (PMU)**

|        |                                                | , ,                            |                            |      |     |         |       |  |  |  |

|--------|------------------------------------------------|--------------------------------|----------------------------|------|-----|---------|-------|--|--|--|

|        | Power Management Base Address + 0X00 (0X40400) |                                |                            |      |     |         |       |  |  |  |

| Symbol |                                                | PMU0 (PMU Control Register 0 ) |                            |      |     |         |       |  |  |  |

| Bit    | [31:24]                                        | [23:20]                        | [19                        | :18] |     | [17:16] |       |  |  |  |

| Name   | MASK                                           | -                              | VD                         | AS   |     | ENVA    |       |  |  |  |

| RW     | R0W-0                                          |                                |                            | RW-0 |     |         |       |  |  |  |

| Bit    | [15:08]                                        | [7:5]                          | [4]                        | [3]  | [2] | [1]     | [0]   |  |  |  |

| Name   | MASK                                           | -                              | - ENBGR ACMS Rsv ENRFO VDD |      |     |         | VDDLP |  |  |  |

| RW     | R0W-0                                          |                                |                            | RW-0 |     |         |       |  |  |  |

| Bit        | Name  | Desc | cription                                                    |

|------------|-------|------|-------------------------------------------------------------|

|            |       | VDD  | A output voltage selection                                  |

|            |       | 00   | VDDA =2.4V                                                  |

| Bit[19~18] | VDAS  | 01   | VDDA =2.7V                                                  |

|            |       | 10   | VDDA =3.0V                                                  |

|            |       | 11   | VDDA =3.3V @ VDD >=3.5V                                     |

|            |       | VDD  | A LDO voltage source configuration for controlling          |

|            |       | The  | output voltage range of the VDDA.                           |

|            |       | 00   | High impedance (High Z)                                     |

| Bit[17~16] | ENVA  |      | Internally short-circuited to the VDD3V;                    |

| DIL[17~10] | ENVA  | 01   | the output of the VDDA is close to the VDD3V                |

|            |       | 10   | Weak pull down; the output of the VDDA is close to the VSS. |

|            |       |      | VDDA LDO; the output of the VDDA can be adjusted            |

|            |       | 11   | , which is decided by the VDAS.                             |

|            |       | Band | d Gap voltage enablement control                            |

| Bit[04]    | ENBGR | 0    | Disable                                                     |

|            |       | 1    | Enable                                                      |

|            |       | ADC  | analog ground input source selection                        |

| Bit[03]    | ACMS  | 0    | External analog ground                                      |

|            |       | 1    | Internal analog ground (used with the ADC)                  |

|            |       | Com  | mon mode voltage (REFO) enablement control                  |

| Bit[01]    | ENRFO | 0    | Disable                                                     |

|            |       | 1    | Enable                                                      |

| VDD18 LDO low-power control |       |                                                            |           |  |  |  |  |  |

|-----------------------------|-------|------------------------------------------------------------|-----------|--|--|--|--|--|

| Bit[00]                     | VDDLP | 0 Normal (the bit should be set as 0 after the SLEEP mode) |           |  |  |  |  |  |

|                             |       | 1                                                          | Low-power |  |  |  |  |  |

## Power management registers PMU1

|        | Power Management Base Address + 0x08 (0x40408) |         |     |     |      |      |  |  |  |  |  |

|--------|------------------------------------------------|---------|-----|-----|------|------|--|--|--|--|--|

| Symbol | PMU1 (PMU Control Register 1)                  |         |     |     |      |      |  |  |  |  |  |

| Bit    |                                                | [31:17] | -   |     |      | [16] |  |  |  |  |  |

| Name   | Rsv                                            |         |     |     |      |      |  |  |  |  |  |

| RW     |                                                | R-0     |     |     |      | R-X  |  |  |  |  |  |

| Bit    | [15:08]                                        | [7:4]   | [3] | [2] | [1]  | [0]  |  |  |  |  |  |

| Name   | MASK LVDS Rsv LVD12 LVDVS F                    |         |     |     |      |      |  |  |  |  |  |

| RW     | R0W-0                                          | RW-0    | R-0 |     | RW-0 |      |  |  |  |  |  |

| Bit        | Name  | Descri | ption                                                            |

|------------|-------|--------|------------------------------------------------------------------|

|            |       |        | LVD Output                                                       |

| Bit[16]    | LVDO  | 0      | When negative voltage > Positive voltage, LVDO=0                 |

|            |       | 1      | When Positive voltage > negative voltage, LVDO=1                 |

|            |       | LVDS   | positive terminal voltage                                        |

|            |       |        | 1.2V,LVDIN, with PT3.4 external voltage source input, set LVDS = |

|            |       | 0000   | 0h                                                               |

|            |       | 0001   | 2.0V                                                             |

|            |       | 0010   |                                                                  |

|            |       |        | 2.2V                                                             |

|            |       | 0100   | 2.3V                                                             |

|            |       | 0101   | 2.4V                                                             |

| Bit[7~4]   | LVDS  | 0110   | 2.5V                                                             |

| וויין דיין |       | 0111   | 2.6V                                                             |

|            |       | 1000   | 2.7V                                                             |

|            |       | 1001   | 2.8V                                                             |

|            |       | 1010   | 2.9V                                                             |

|            |       | 1011   | 3.0V                                                             |

|            |       | 1100   | 3.1V                                                             |

|            |       | 1101   | 3.2V                                                             |

|            |       | 1110   | 3.3V                                                             |

|            |       | 1111   | 3.4V                                                             |

|            |       | LVD ne | egative voltage source                                           |

| Bit[02]    | LVD12 | 0      | V12_BOR                                                          |

|            |       | 1      | V12_BGR(form bandgap output, precise)                            |

|            |       | LVD P  | ositive voltage source                                           |

| Bit[01]    | LVDVS | 0      | VDD3V                                                            |

|            |       | 1      | VLCD                                                             |

|            |       | LVD E  | nable                                                            |

| Bit[00]    | ENLVD | 0      | Disable                                                          |

|            |       | 1      | Enable                                                           |

#### 6. CLOCK SYSTEM

#### 6.1. Overall description

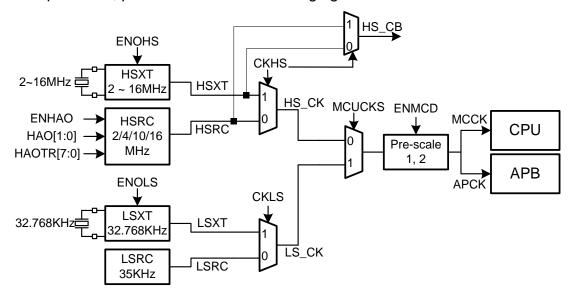

The clock control system provides the clocks for the whole chip, including the system clocks (CPU clock, APB clock) and all peripheral operating clocks (timer, communication interface, RTC, analog circuit, etc.) Each function module has a clock switch controller, clock source selection and frequency divider. Under the SLEEP mode, the controller always closes the external crystal oscillators, internal crystal oscillators and system clocks to minimize the system power consumption.

The operating clock sources include the external crystal oscillators, internal HAO and LPO oscillators; with the frequency divider, the frequency sources of the CPU and the peripheral devices can be flexibly allocated and managed to adjust the power consumption of the chip in order to save the energy.

#### 6.1.1. External oscillators

There are two external oscillators, including the high-speed crystal oscillator (HSXT) and the low-speed crystal oscillator (LSXT). The chip has two independent input pins for the external high-speed crystal oscillator and low-speed crystal oscillator; thus, the user can connect the two external oscillators to the chip at the same time. The external oscillator should be connected to a resistor in parallel, or the crystal oscillator will not work even if it is soldered at the pin; besides, the crystal oscillator is connected to two 0~20pF ground capacitors and the capacitance of each capacitor is subject to the parasitic capacitor caused by the layout of the PCB.

The parallel resistor between the pins of the oscillator and the capacitor C2/C1 parameters of each pin of the oscillator will vary with the frequency, brand of the external crystal oscillator and the layout of the PCB. The following table lists suggested allocation of the R1/C1/C2 parameters and the frequency sources for your reference. In the absence of special circumstances, it can also be capacitive default.

| Туре       | Symbol | External   | crystal osci | Instruction execution status |      |       |           |

|------------|--------|------------|--------------|------------------------------|------|-------|-----------|

|            |        | Frequency  | R1/Ω         | C1                           | C2   | Sleep | Idle      |

|            |        | requericy  | 1 (1/22      | 5                            | 02   | mode  | mode      |

| Low-speed  | LSXT   | 32768Hz    | 10M          | 10pF                         | 10pF | Stop  | Available |

| oscillator | LOXI   | 327 001 12 | TOIVI        | τορι                         | ΙΟΡΙ | σιορ  | Available |

| High-speed | HSXT   | 2~16MHz    | 1M           | 10pF                         | 10pF | Stop  | Available |

| oscillator |        |            |              | •                            | •    | •     |           |

6-1 Suggest external crystal oscillator configuration

Note: The external oscillator pin capacitance (C1 / C2 parameters) can be in accordance with the actual PCB board layout with a different crystal as the case may choose to adjust

the capacitance value of the size, it is recommended in the range of 0 ~ 20pF. Using an external crystal oscillator parameter Note:

- (01) when using 16MHz, chip operating voltage must be greater than 3.0V.

- (02) The external crystal shock 4MHz / 8MHz stabilization time is about 30ms.

- (03) External 32768Hz crystal shock stabilization time is about 1.3s.

- (04) After Sleep instruction execution, external crystal earthquake shock all stops.

- (05) When External crystal oscillator parameter, note that the pin input / output configuration, the use shall not be required to set the configuration pin internal pullup resistor, in order to avoid abnormal operation. And the external resistor R1 must not default. (06) To use an external oscillator (HSXT), recommended to choose the MCU clock / 2, can reduce the oscillator frequency source interference, and strengthen anti-jamming capability.

#### 6.1.2. Internal crystal oscillators HAO and LPO

The HAO is an external high-speed RC oscillator of the chip and its typical output frequency is 2MHz/4MHz/10MHz/16MHz; besides, it has several features, such as quick start, high anti-interference and low power consumption, etc. The output frequency of the HAO is adjustable; therefore, the user can adjust the output frequency of the HAO by software.

#### Matter needing attentions of using internal crystal oscillators:

- The operating voltage of the chip should be kept high when using the 16MHz HAO.

- The output frequency of the HAO can be adjusted by modifying the register HAOTR 0x40304[7:0] Example: When set HAO work at 2MHz, if the actual output is only 1.99MHz, it can be controlled by adjusting the position HAOTR [7:0] to adjust the frequency of the output, HAOTR default is 0x80, adjustments can be increased up HAO actual operating frequency.

- The default oscillator of the chip is the internal 2MHz HAO; the user can modify the default settings register 0x40300[4:3] to change the output frequencies of other HAOs.

- The stabilization time of the 4MHz HAO is about 0.5ms;

- After the SLEEP instruction is executed, all HAO oscillators will stop and enter the SLEEP mode.

- From Sleep mode to wake up time of about 1024 \* HAO + 2048 \* LPO = <64ms.</li>

Note: If you meet the above description wake-up time, it should be before entering Sleep Mode, CPU frequency source is selected as HAO.

- After the IDLE instruction is executed, all HAO oscillators will not stop, but the CPU will enter the IDLE mode.

- From Idle Mode to wake-up time of about 500 cycles, when using a preset HAO = CPU Clock when 2MHz, wake-up time is about 250us.

The LPO is the internal low-speed RC oscillator of the chip; its output frequency is 35 kHz and has low power consumption; it will immediately start after the chip is power-on or wakened; besides, it cannot be enabled; in other words, the LPO will keep working during the whole operation process of the chip.

The stabilization time of the LPO is about 510us and it is the only operating clock source of the WDT.

- After the SLEEP instruction is executed, all LPO oscillators will stop.

- After the IDLE instruction is executed, all LPO oscillators will not stop, but the CPU will

enter the IDLE mode.

- From Idle Mode to wake-up time of about 500 cycles, when the CPU Clock using a preset LPO = 35 kHz, wake-up time of about 14ms.

Typical output frequencies of the HAO and LPO are as shown in following Table 6-2.

| Symbol   | Frequency  | Frequenc                | cy source con | Instruction execution status |       |           |

|----------|------------|-------------------------|---------------|------------------------------|-------|-----------|

| Syllibol | rrequericy |                         |               |                              | Sia   | ilus      |

|          |            | ENHAO[1]                | HAO[1:0]      | CKHS[1]                      | Sleep | ldle      |

|          | 2MHz       | 1                       | 00B           | 0                            | Stop  | Workable  |

| HAO      | 4MHz       | 1                       | 01B           | 0                            | Stop  | Workable  |

| ПАО      | 10MHz      | 1                       | 1 10B         |                              | Stop  | Workable  |

|          | 16MHz      | 1                       | 1 11B         |                              | Stop  | Workable  |

| LPO      | 35KHz      | Start after the chip is |               | CKLS=0                       | Stop  | Oscillate |

|          | JUNITZ     | powe                    | er-on         | UNLO=0                       | SiOp  | Oscillate |

Table 6-2 internal crystal oscillator configuration

#### **HAO** calibration method:

Chip HAO will have about +/- 10% error range, If the user wants a more accurate HAO operating frequency, the HYCON C library can be calibrated (DrvCLOCK\_CalibrateHAO this function), This function can be set to control the HAO oscillation frequency error within the range of +/- 2%, Detailed HAO frequency specifications, refer to the document DS-HY16F3981\_EN Note.

-function

void DrvCLOCK\_CalibrateHAO (short int uMHz)

- Function

HAO calibration function; Note To correspond with the selected HAO frequency use; setting register 0x40304 [7: 0] value

-Input parameters

uMHz [in] pending correction of HAO frequency mode selection

0: Correction 2MHz; 1: Correction 4MHz; 2: Correction 10MHz; 3: Correction 16MHz;

#### 6.1.3. CPU and external peripheral operating frequency sources configuration

Both of the external and internal crystal oscillators can provide the frequency sources for the CPU and the frequency sources will be provided for the CPU after passing the frequency dividers. The chip can determine the frequency source of the CPU is the HS\_CK or LS\_CK via the frequency selector MCUCKS [1] and perform the frequency division via the frequency divider ENMCD [1]. Thus, there are multiple operating frequency modes for the CPU to select from to determine the instruction cycle of the chip.

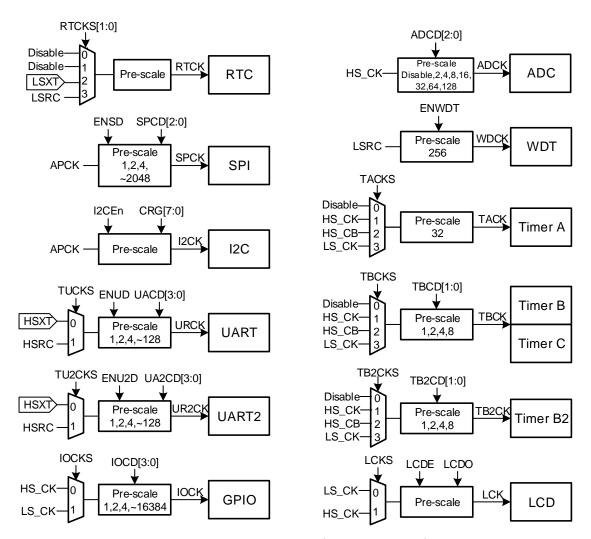

Similarly, the external peripheral operating frequency sources are also provided by the external, internal crystal oscillators and the HS\_CK or LS\_CK passing the frequency dividers; or the frequency sources can be directly provided by the crystal oscillators, such as the WDT. As the external peripheral operating frequency configuration may vary with the different operations, please refer to the following figure for more information.

Table 6-1 CPU operating frequency source configuration diagram

Table 6-2 External peripheral operating frequency configuration diagram

#### 6.2. Register address

| Clock Register Address            | 31 24      | 23   16 | 15 8  | 7 0   |  |

|-----------------------------------|------------|---------|-------|-------|--|

| CLK Base Address + 0x00 (0x40300) | -          | -       | MASK0 | REG0  |  |

| CLK Base Address + 0x04 (0x40304) | -          | -       | -     | HAOTR |  |

| CLK Base Address + 0x08 (0x40308) | MASK1 REG1 |         | MASK2 | REG2  |  |

| CLK Base Address + 0x0C (0x4030C) | MASK3      | REG3    | MASK4 | REG4  |  |

| CLK Base Address + 0x10 (0x40310) | MASK5      | REG5    | MASK6 | REG6  |  |

| CLK Base Address + 0x14 (0x40314) | -          | -       | MASK7 | REG7  |  |

-Reserved

# 6.3. Register function

# 6.3.1. Clock system register CLKCR0

|        | Clock Base Address + 0x00 (0x40300) |                                 |      |      |       |       |       |       |  |  |  |  |

|--------|-------------------------------------|---------------------------------|------|------|-------|-------|-------|-------|--|--|--|--|

| Symbol |                                     | CLK0 (Clock Control Register 0) |      |      |       |       |       |       |  |  |  |  |

| Bit    |                                     | [31:16]                         |      |      |       |       |       |       |  |  |  |  |

| Name   |                                     | RSV(Reserved)                   |      |      |       |       |       |       |  |  |  |  |

| RW     |                                     |                                 |      | R-0  |       |       |       |       |  |  |  |  |

| Bit    | [15:8]                              | [7]                             | [6]  | [5]  | [4:3] | [2]   | [1]   | [0]   |  |  |  |  |

| Name   | MASK                                | OHS_HS                          | CKLS | CKHS | HAO   | ENOLS | ENOHS | ENHAO |  |  |  |  |

| RW     | R0W-0                               |                                 |      | RV   | V-0   |       |       | RW-1  |  |  |  |  |

| Bit      | Name   | Description                                       |                                              |  |  |  |  |

|----------|--------|---------------------------------------------------|----------------------------------------------|--|--|--|--|

|          | OHS_HS | Exter                                             | External oscillator mode selection           |  |  |  |  |

| Bit[7]   |        | 0                                                 | HSXT<4MHz                                    |  |  |  |  |

|          |        | 1                                                 | HSXT>4MHz                                    |  |  |  |  |

|          |        | Chip                                              | low-speed frequency source selection         |  |  |  |  |

| Bit[6]   | CKLS   | 0                                                 | Internal low-speed oscillator (OSC_LSRC)     |  |  |  |  |

|          |        | 1                                                 | External low-speed oscillator (OSC_LSXT)     |  |  |  |  |

|          |        | Chip high-speed frequency source selection        |                                              |  |  |  |  |

| Bit[5]   | CKHS   | 0                                                 | External low-speed oscillator (OSC_HSRC)     |  |  |  |  |

|          |        | 1                                                 | External high-speed oscillator (OSC_HSXT)    |  |  |  |  |

|          |        | Internal high-speed oscillator mode configuration |                                              |  |  |  |  |

|          | НАО    | [00]                                              | 2MHz                                         |  |  |  |  |

| Bit[4~3] |        | [01]                                              | 4MHz                                         |  |  |  |  |

|          |        | [10]                                              | 10MHz                                        |  |  |  |  |

|          |        | [11]                                              | 16MHz                                        |  |  |  |  |

|          | ENOLS  | Exter                                             | nal low-speed oscillator enablement control  |  |  |  |  |

| Bit[02]  |        | 0                                                 | Disable                                      |  |  |  |  |

|          |        | 1                                                 | Enable                                       |  |  |  |  |

|          | ENOHS  | Exter                                             | nal high-speed oscillator enablement control |  |  |  |  |

| Bit[01]  |        | 0                                                 | Disable                                      |  |  |  |  |

|          |        | 1                                                 | Enable                                       |  |  |  |  |

|          | ENHAO  | Internal high-speed oscillator enablement control |                                              |  |  |  |  |

| Bit[00]  |        | 0                                                 | Disable                                      |  |  |  |  |

|          |        | 1                                                 | Enable                                       |  |  |  |  |

#### Precautions:

HS\_CK, LS\_CK clock source foolproof control:

When using CKHS (or CKLS) switch to the HS\_CK (or LS\_CK) clock source, it judges the corresponding oscillator Enable or Disable. If it is Disable, it will not perform switching clock source.

#### Precautions:

HS\_CK, LS\_CK clock source foolproof closed:

If user would like to disable one of the oscillator, have to switch HS\_CK (or LS\_CK) to another one enabling oscillator. In order to avoid the system no clock source that cause system crash.

#### Precautions:

Disable high-speed oscillator foolproof control:

Two sets of high-speed oscillators can be disabled at the same time, but user needs to switch the CPU Core to low-speed clock source. Otherwise, user cannot disable the two sets of high-speed oscillators at the same time.

#### 6.3.2. Clock system register CLKCR1

| Clock Base Address + 0x04 (0x40304) |                                 |        |  |  |  |  |

|-------------------------------------|---------------------------------|--------|--|--|--|--|

| Symbol                              | CLK1 (Clock Control Register 1) |        |  |  |  |  |

| Bit                                 | [31                             | :16]   |  |  |  |  |

| Name                                | Res                             | erved  |  |  |  |  |

| RW                                  | R                               | R-0    |  |  |  |  |

| Bit                                 | [15:8]                          | [7:0]  |  |  |  |  |

| Name                                | Reserved                        | HAOTR  |  |  |  |  |

| RW                                  | R-0                             | RW-80H |  |  |  |  |

| Bit      | Name  | Description |                                                             |  |  |

|----------|-------|-------------|-------------------------------------------------------------|--|--|

|          |       | Inter       | Internal high-speed oscillator calibration control register |  |  |

| Bit[7:0] | HAOTR | 0           | Set 0                                                       |  |  |

|          |       | 1           | Set 1                                                       |  |  |

1\*LSB.Step = 0.125%

0000\_0000 is the lowest speed.

1000\_0000 is the default speed.

1111\_1111 is the higher speed.

**Description:** HAO frequency correction, Use the HYCON C library

DrvCLOCK\_CalibrateHAO this function, The Trim value of the HAO is written to the

HAOTR register to control the HAO frequency error within +/- 2%

#### 6.3.3. Clock system register CLKCR2

|        | Clock Base Address + 0x08 (0x40308) |         |                       |             |      |              |        |            |

|--------|-------------------------------------|---------|-----------------------|-------------|------|--------------|--------|------------|

| Symbol | CLKCR2 (Clock Control Register 2)   |         |                       |             |      |              |        |            |

| Bit    | [31:24]                             | [23:22] | [21]                  | [20]        | [19] |              | [18:16 | <b>i</b> ] |

| Name   | MASK                                | RTCKS   | TUCKS                 | <b>ENUD</b> | Rsv  | UACD         |        |            |

| RW     | R0W-0                               | RW-0    | RW                    | <b>/-</b> 0 | R-0  | RW-0         |        |            |

| Bit    | [15:08]                             | [7:6]   | [5:                   | 4]          | [3   | 3:2] [1] [0] |        | [0]        |

| Name   | MASK                                | TBCKS   | TBCD TACKS ENMCD MCUC |             |      | MCUCKS       |        |            |

| RW     | R0W-0                               | RW-0    |                       |             |      |              |        |            |

| Bit        | Name  | Description                                                |  |  |  |

|------------|-------|------------------------------------------------------------|--|--|--|

|            | RTCKS | RTC clock source control                                   |  |  |  |

|            |       | 00 Disable                                                 |  |  |  |

| Bit[23~22] |       | 01 Disable                                                 |  |  |  |

|            |       | 10 LSXT(LSXT to be enabled, otherwise regarded as Disable) |  |  |  |

|            |       | 11 LPO                                                     |  |  |  |

| Di+[04]    | TUCKS | EUART clock source selection                               |  |  |  |

| Bit[21]    |       | 0 HSXT: External high-speed oscillator                     |  |  |  |

|            |        | HSRC: Internal high-speed oscillator                                   |

|------------|--------|------------------------------------------------------------------------|

|            |        | EUART clock source enablement control                                  |

| Bit[20]    | ENUD   | 0 Disable                                                              |

|            | LINOD  | 1 Enable                                                               |

|            |        | EUART clock source frequency divider configuration                     |

|            |        | 0000 EUART clock source/ 1                                             |

|            |        | 0001 EUART clock source/ 2                                             |

|            |        | 0010 EUART clock source/ 4                                             |

| Bit[18~16] | UACD   | 0011 EUART clock source/ 8                                             |

|            | 07.02  | 0100 EUART clock source/ 16                                            |

|            |        | 0101 EUART clock source/ 32                                            |

|            |        | 0110 EUART clock source/ 64                                            |

|            |        | 0111 EUART clock source/ 128                                           |

|            |        | Timer B,C clock source selection                                       |

|            |        | 00 Disable                                                             |

| Bit[7~6]   | TBCKS  | 01 HS_CK                                                               |

|            |        | 10 HS_CB                                                               |

|            |        | 11 LS_CK                                                               |

|            |        | Timer B,C clock source frequency divider configuration                 |

|            | TBCD   | 00 TBCK/1                                                              |

| Bit[5~4]   |        | 01 TBCK/2                                                              |

|            |        | 10 TBCK/4                                                              |

|            |        | 11   TBCK/8                                                            |

|            | TACKS  | Timer A clock source selection, the frequency divider is fixed to 1/32 |

|            |        | 0 Disable                                                              |

| Bit[3~2]   |        | 1 HS CK                                                                |

| Dit[3~2]   |        | HS_CB ( If the MCU to HAO as the clock source, TMA to HSXT             |

|            |        | 2 as the clock, and vice versa)                                        |

|            |        | 3 LS_CK                                                                |

|            | ENMCD  | MCU input clock frequency setting                                      |

| Bit[01]    |        | 0 MCU Clock/1                                                          |

|            |        | 1 MCU Clock/2                                                          |

|            | MCUCKS | MCU input clock source selection                                       |

| Bit[00]    |        | ·                                                                      |

| Dit[OO]    |        | 1 LS_CK                                                                |

|            |        | I LO_UN                                                                |

# 6.3.4. Clock system register CLKCR3

|        | Clock Base Address + 0x0C (0x4030C) |                                   |                 |      |      |       |  |  |

|--------|-------------------------------------|-----------------------------------|-----------------|------|------|-------|--|--|

| Symbol |                                     | CLKCR3 (Clock Control Register 3) |                 |      |      |       |  |  |

| Bit    | [31:24]                             | [31:24] [23:21] [20] [19:16]      |                 |      |      |       |  |  |

| Name   | MASK                                | -                                 | IOCKS           | IOCD |      |       |  |  |

| RW     | R0W-0                               | -                                 | RW-0            |      |      |       |  |  |

| Bit    | [15:08]                             | [7]                               | [6:4] [3] [2:0] |      |      | [2:0] |  |  |

| Name   | MASK                                | -                                 | ADCD ENSD       |      | ENSD | SPCD  |  |  |

| RW     | R0W-0                               | R-0                               | RW-0            |      |      |       |  |  |

| Bit        | Name  | Description                               |                                     |  |  |

|------------|-------|-------------------------------------------|-------------------------------------|--|--|

| Dit        | Name  | GPIO input clock source selection         |                                     |  |  |

| Bit[20]    | IOCKS | 0 HS_CK                                   |                                     |  |  |

|            |       | 1                                         | LS_CK                               |  |  |

|            |       | GPIO clo                                  | ock frequency divider configuration |  |  |

|            |       | 0000                                      | Disable                             |  |  |

|            |       | 0001                                      | GPIO clock source/ 1                |  |  |

|            |       | 0010                                      | GPIO clock source/ 2                |  |  |

|            |       | 0011                                      | GPIO clock source/ 4                |  |  |

|            |       | 0100                                      | GPIO clock source/ 8                |  |  |

|            |       | 0101                                      | GPIO clock source/ 16               |  |  |

|            |       | 0110                                      | GPIO clock source/ 32               |  |  |

| Bit[19~16] | IOCD  | 0111                                      | GPIO clock source/ 64               |  |  |

|            |       | 1000                                      | GPIO clock source/ 128              |  |  |

|            |       | 1001                                      | GPIO clock source/ 256              |  |  |

|            |       | 1010                                      | GPIO clock source/ 512              |  |  |

|            |       | 1011                                      | GPIO clock source/ 1024             |  |  |

|            |       | 1100                                      | GPIO clock source/ 2048             |  |  |

|            |       | 1101                                      | GPIO clock source/ 4096             |  |  |

|            |       | 1110                                      | GPIO clock source/ 8192             |  |  |

|            |       | 1111                                      | GPIO clock source/ 16384            |  |  |

|            | ADCD  | ADC clo                                   | ck frequency divider configuration  |  |  |

|            |       | 000                                       | Disable                             |  |  |

|            |       | 001                                       | Reserved                            |  |  |

|            |       | 010                                       | ~HS_CK / 4                          |  |  |

| Bit[6~4]   |       | 011                                       | ~HS_CK / 8                          |  |  |

|            |       | 100                                       | ~HS_CK / 16                         |  |  |

|            |       | 101                                       | ~HS_CK / 32                         |  |  |

|            |       | 110                                       | ~HS_CK / 64                         |  |  |

|            |       | 111                                       | ~HS_CK / 128                        |  |  |

| Bit[3]     | ENSD  | SPI clock switch                          |                                     |  |  |

|            |       | 0                                         | Disable                             |  |  |

|            |       | 1                                         | Enable                              |  |  |

|            | SPCD  | SPI clock frequency divider configuration |                                     |  |  |

| Bit[2~0]   |       | 000                                       | Reserved                            |  |  |

| Dit[2 0]   |       | 001                                       | SPI clock source/ 2                 |  |  |

|            |       | 010                                       | SPI clock source/ 4                 |  |  |

| 01  | 1 S  | SPI clock source/ 8   |

|-----|------|-----------------------|

| 100 | 00 S | SPI clock source/ 32  |

| 10  | 1 S  | PI clock source/ 128  |

| 110 | 0 S  | PI clock source/ 512  |

| 111 | 1 S  | PI clock source/ 2048 |

Note: Suggest user to set ADC clock working on the 1MHz

EX: HS\_CK=4MHz, ADCD working frequency as HS\_CK/4=1MHz

# 6.3.5. Clock system register CLKCR4

| Clock Base Address + 0x10 (0x40310) |                                   |                     |      |      |       |         |  |  |  |

|-------------------------------------|-----------------------------------|---------------------|------|------|-------|---------|--|--|--|

| Symbol                              | CLKCR4 (Clock Control Register 4) |                     |      |      |       |         |  |  |  |

| Bit                                 | [31:24]                           | [23:22]             | [21] | [20] | [19]  | [18:16] |  |  |  |

| Name                                | MASK                              | LCDCPD UT2CKS ENU2D |      |      | -     | UA2CD   |  |  |  |

| RW                                  | R0W-0                             |                     | RW-0 |      | -     | RW-0    |  |  |  |

| Bit                                 | [15:08]                           | [7]                 | [6:  | 4]   | [3:1] | [0]     |  |  |  |

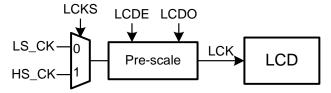

| Name                                | MASK                              | -                   | LCDO |      | LCDE  | LCKS    |  |  |  |

| RW                                  | R0W-0                             | -                   | RW-0 |      |       |         |  |  |  |

| Bit        | Name   | Des                                                | scription                                              |  |  |  |  |  |  |  |

|------------|--------|----------------------------------------------------|--------------------------------------------------------|--|--|--|--|--|--|--|

|            |        | LCI                                                | _CD charge pump regulator clock source selection       |  |  |  |  |  |  |  |

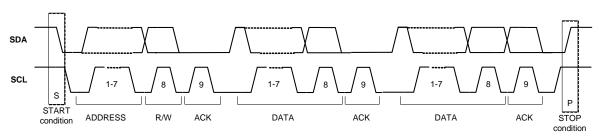

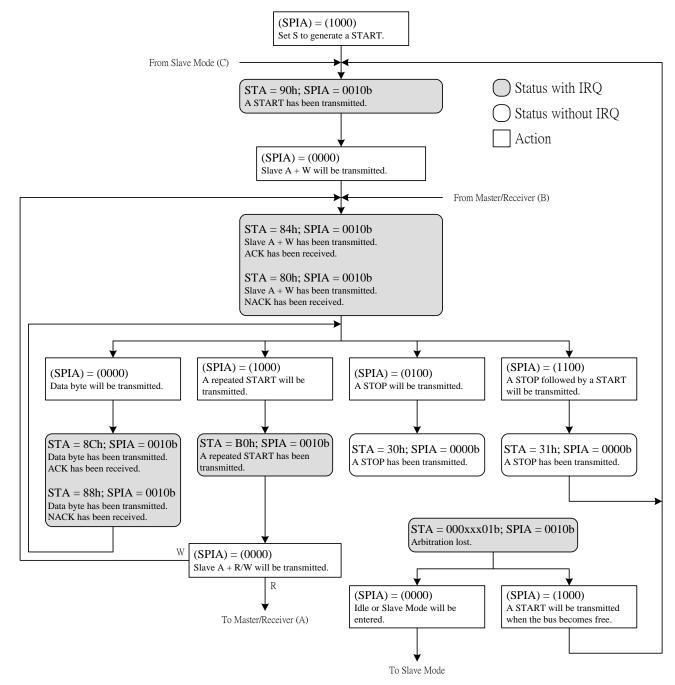

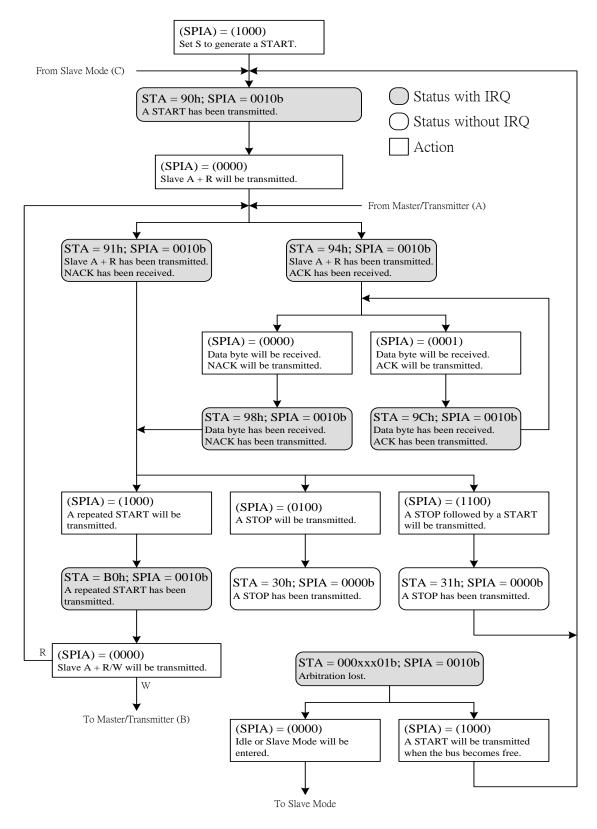

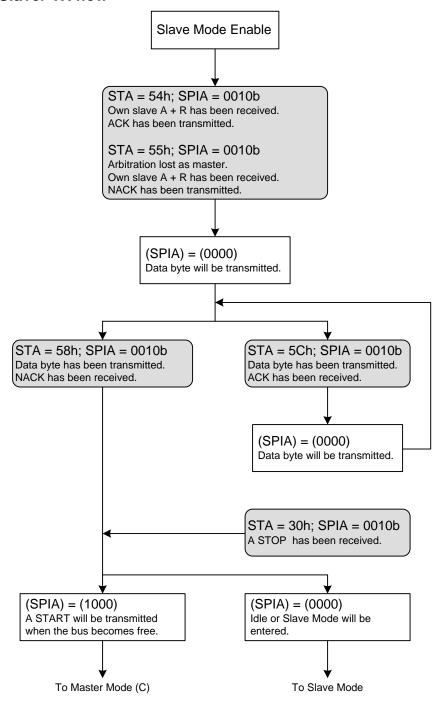

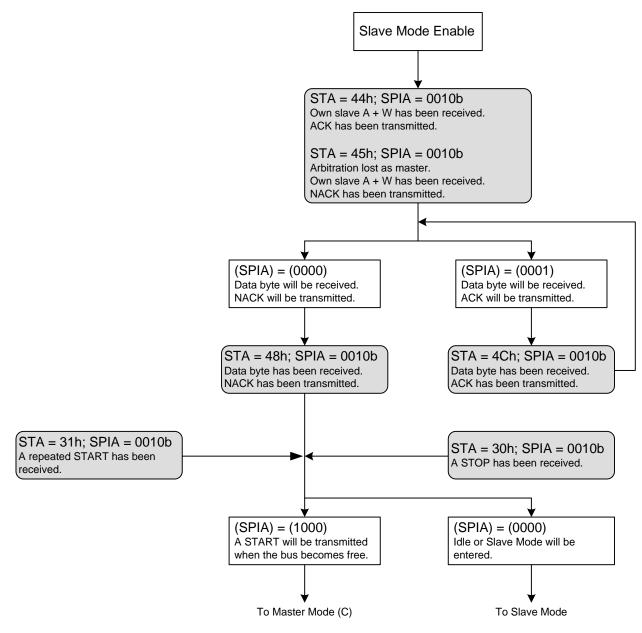

|            |        | 0                                                  | LS_CK / 1 or HS_CK/8 (LCKS determines LS_CK or HS_CK)  |  |  |  |  |  |  |  |